https://www.fpgamall.com

# THE DATASHEET OF FPGA

# **Stratix V Device Datasheet**

SV53001-4.1

This document covers the electrical and switching characteristics for Stratix<sup>®</sup> V devices. Electrical characteristics include operating conditions and power consumption. Switching characteristics include transceiver specifications, core, and periphery performance. This document also describes I/O timing, including programmable I/O element (IOE) delay and programmable output buffer delay.

For information regarding the densities and packages of devices in the Stratix V family, refer to the *Stratix V Device Overview*.

# **Electrical Characteristics**

The following sections describe the electrical characteristics of Stratix V devices.

# **Operating Conditions**

When you use Stratix V devices, they are rated according to a set of defined parameters. To maintain the highest possible performance and reliability of Stratix V devices, you must consider the operating requirements described in this chapter.

Stratix V devices are offered in commercial and industrial temperature grades.

Commercial devices are offered in -1 (fastest), -2, -3, and -4 core speed grades. Industrial devices are offered in -2, -3, and -4 core speed grades. Stratix V E devices are offered based on core speed grades while Stratix V GX, GS, and GT devices are also offered in -1, -2, and -3 transceiver speed grades.

Table 1 lists the industrial and commercial speed grades for the Stratix V GX and Stratix V GS devices.

Table 1. Stratix V GX and GS Commercial and Industrial Speed Grade Offering (1), (2), (3) (Part 1 of 2)

| Transceiver Speed         | Core Speed Grade |         |     |    |         |         |      |    |

|---------------------------|------------------|---------|-----|----|---------|---------|------|----|

| Grade                     | C1               | C2, C2L | C3  | C4 | 12, 12L | 13, 13L | I3YY | 14 |

| 1<br>GX channel—14.1 Gbps | Yes              | Yes     | _   | _  | Yes     | _       | _    | _  |

| 2<br>GX channel—12.5 Gbps | Yes              | Yes     | Yes | _  | Yes     | Yes     | _    | _  |

© 2019 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Page 2 Electrical Characteristics

Table 1. Stratix V GX and GS Commercial and Industrial Speed Grade Offering (1), (2), (3) (Part 2 of 2)

| Transceiver Speed        |    |         |     | Core Spe | ed Grade |         |                    |     |

|--------------------------|----|---------|-----|----------|----------|---------|--------------------|-----|

| Grade                    | C1 | C2, C2L | C3  | C4       | 12, 12L  | 13, 13L | I3YY               | 14  |

| 3<br>GX channel—8.5 Gbps | _  | Yes     | Yes | Yes      | _        | Yes     | Yes <sup>(4)</sup> | Yes |

#### Notes to Table 1:

- (1) C = Commercial temperature grade; I = Industrial temperature grade.

- (2) Lower number refers to faster speed grade.

- (3) C2L, I2L, and I3L speed grades are for low-power devices.

- (4) I3YY speed grades can achieve up to 10.3125 Gbps.

Table 2 lists the industrial and commercial speed grades for the Stratix V GT devices.

Table 2. Stratix V GT Commercial and Industrial Speed Grade Offering (1), (2)

| Transacius Snood Crada                             | Core Speed Grade |     |     |     |  |  |  |

|----------------------------------------------------|------------------|-----|-----|-----|--|--|--|

| Transceiver Speed Grade                            | C1               | C2  | 12  | 13  |  |  |  |

| 2<br>GX channel—12.5 Gbps<br>GT channel—28.05 Gbps | Yes              | Yes | _   | _   |  |  |  |

| 3<br>GX channel—12.5 Gbps<br>GT channel—25.78 Gbps | Yes              | Yes | Yes | Yes |  |  |  |

#### Notes to Table 2:

- (1) C = Commercial temperature grade; I = Industrial temperature grade.

- (2) Lower number refers to faster speed grade.

# **Absolute Maximum Ratings**

Absolute maximum ratings define the maximum operating conditions for Stratix V devices. The values are based on experiments conducted with the devices and theoretical modeling of breakdown and damage mechanisms. The functional operation of the device is not implied for these conditions.

Conditions other than those listed in Table 3 may cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse effects on the device.

Table 3. Absolute Maximum Ratings for Stratix V Devices (Part 1 of 2)

| Symbol              | Description                                                            | Minimum | Maximum | Unit |

|---------------------|------------------------------------------------------------------------|---------|---------|------|

| V <sub>CC</sub>     | Power supply for core voltage and periphery circuitry                  | -0.5    | 1.35    | V    |

| V <sub>CCPT</sub>   | Power supply for programmable power technology                         | -0.5    | 1.8     | V    |

| V <sub>CCPGM</sub>  | Power supply for configuration pins                                    | -0.5    | 3.9     | V    |

| V <sub>CC_AUX</sub> | Auxiliary supply for the programmable power technology                 | -0.5    | 3.4     | V    |

| V <sub>CCBAT</sub>  | Battery back-up power supply for design security volatile key register | -0.5    | 3.9     | V    |

| V <sub>CCPD</sub>   | I/O pre-driver power supply                                            | -0.5    | 3.9     | V    |

| V <sub>CCIO</sub>   | I/O power supply                                                       | -0.5    | 3.9     | V    |

Table 3. Absolute Maximum Ratings for Stratix V Devices (Part 2 of 2)

| Symbol                | Description                    | Minimum         | Maximum | Unit |

|-----------------------|--------------------------------|-----------------|---------|------|

| V <sub>CCD_FPLL</sub> | PLL digital power supply       | -0.5            | 1.8     | V    |

| V <sub>CCA_FPLL</sub> | PLL analog power supply        | -0.5            | 3.4     | V    |

| V <sub>I</sub>        | DC input voltage               | -0.5            | 3.8     | V    |

| T <sub>J</sub>        | Operating junction temperature | <del>-</del> 55 | 125     | °C   |

| T <sub>STG</sub>      | Storage temperature (No bias)  | -65             | 150     | °C   |

| I <sub>OUT</sub>      | DC output current per pin      | -25             | 40      | mA   |

Table 4 lists the absolute conditions for the transceiver power supply for Stratix V GX, GS, and GT devices.

Table 4. Transceiver Power Supply Absolute Conditions for Stratix V GX, GS, and GT Devices

| Symbol                | Description                                                  | Devices    | Minimum | Maximum | Unit |

|-----------------------|--------------------------------------------------------------|------------|---------|---------|------|

| V <sub>CCA_GXBL</sub> | Transceiver channel PLL power supply (left side)             | GX, GS, GT | -0.5    | 3.75    | V    |

| V <sub>CCA_GXBR</sub> | Transceiver channel PLL power supply (right side)            | GX, GS     | -0.5    | 3.75    | V    |

| V <sub>CCA_GTBR</sub> | Transceiver channel PLL power supply (right side)            | GT         | -0.5    | 3.75    | V    |

| V <sub>CCHIP_L</sub>  | Transceiver hard IP power supply (left side)                 | GX, GS, GT | -0.5    | 1.35    | V    |

| V <sub>CCHIP_R</sub>  | Transceiver hard IP power supply (right side)                | GX, GS, GT | -0.5    | 1.35    | V    |

| V <sub>CCHSSI_L</sub> | Transceiver PCS power supply (left side)                     | GX, GS, GT | -0.5    | 1.35    | V    |

| V <sub>CCHSSI_R</sub> | Transceiver PCS power supply (right side)                    | GX, GS, GT | -0.5    | 1.35    | V    |

| V <sub>CCR_GXBL</sub> | Receiver analog power supply (left side)                     | GX, GS, GT | -0.5    | 1.35    | V    |

| V <sub>CCR_GXBR</sub> | Receiver analog power supply (right side)                    | GX, GS, GT | -0.5    | 1.35    | V    |

| V <sub>CCR_GTBR</sub> | Receiver analog power supply for GT channels (right side)    | GT         | -0.5    | 1.35    | V    |

| V <sub>CCT_GXBL</sub> | Transmitter analog power supply (left side)                  | GX, GS, GT | -0.5    | 1.35    | V    |

| V <sub>CCT_GXBR</sub> | Transmitter analog power supply (right side)                 | GX, GS, GT | -0.5    | 1.35    | V    |

| V <sub>CCT_GTBR</sub> | Transmitter analog power supply for GT channels (right side) | GT         | -0.5    | 1.35    | V    |

| V <sub>CCL_GTBR</sub> | Transmitter clock network power supply (right side)          | GT         | -0.5    | 1.35    | V    |

| V <sub>CCH_GXBL</sub> | Transmitter output buffer power supply (left side)           | GX, GS, GT | -0.5    | 1.8     | V    |

| V <sub>CCH_GXBR</sub> | Transmitter output buffer power supply (right side)          | GX, GS, GT | -0.5    | 1.8     | V    |

# **Maximum Allowed Overshoot and Undershoot Voltage**

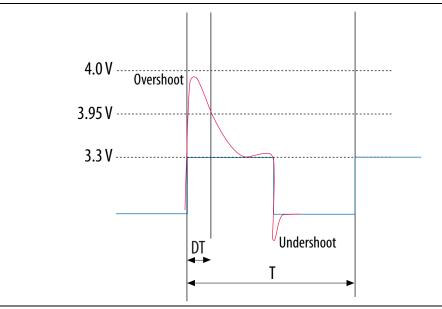

During transitions, input signals may overshoot to the voltage shown in Table 5 and undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

Page 4 Electrical Characteristics

Table 5 lists the maximum allowed input overshoot voltage and the duration of the overshoot voltage as a percentage of device lifetime. The maximum allowed overshoot duration is specified as a percentage of high time over the lifetime of the device. A DC signal is equivalent to 100% of the duty cycle. For example, a signal that overshoots to 3.95 V can be at 3.95 V for only  $\sim 21\%$  over the lifetime of the device; for a device lifetime of 10 years, the overshoot duration amounts to  $\sim 2$  years.

**Table 5. Maximum Allowed Overshoot During Transitions**

| Symbol  | Description      | Condition (V) | Overshoot Duration as %<br>@ T <sub>J</sub> = 100°C | Unit |   |

|---------|------------------|---------------|-----------------------------------------------------|------|---|

|         |                  | 3.8           | 100                                                 | %    |   |

|         |                  | 3.85          | 64                                                  | %    |   |

|         |                  |               | 3.9                                                 | 36   | % |

|         |                  | 3.95          | 21                                                  | %    |   |

| Vi (AC) | AC input voltage | 4             | 12                                                  | %    |   |

|         |                  | 4.05          | 7                                                   | %    |   |

|         |                  | 4.1           | 4                                                   | %    |   |

|         |                  | 4.15          | 2                                                   | %    |   |

|         |                  | 4.2           | 1                                                   | %    |   |

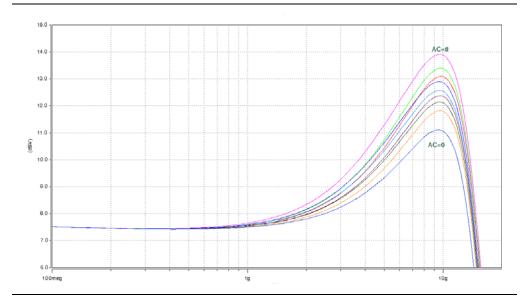

Figure 1. Stratix V Device Overshoot Duration

# **Recommended Operating Conditions**

This section lists the functional operating limits for the AC and DC parameters for Stratix V devices. Table 6 lists the steady-state voltage and current values expected from Stratix V devices. Power supply ramps must all be strictly monotonic, without plateaus.

Table 6. Recommended Operating Conditions for Stratix V Devices (Part 1 of 2)

| Symbol                 | Description                                                                                            | Condition  | Min <sup>(4)</sup> | Тур  | Max <sup>(4)</sup> | Unit |

|------------------------|--------------------------------------------------------------------------------------------------------|------------|--------------------|------|--------------------|------|

|                        | Core voltage and periphery circuitry power supply (C1, C2, I2, and I3YY speed grades)                  | _          | 0.87               | 0.9  | 0.93               | V    |

| V <sub>CC</sub>        | Core voltage and periphery circuitry power supply (C2L, C3, C4, I2L, I3, I3L, and I4 speed grades) (3) | _          | 0.82               | 0.85 | 0.88               | V    |

| V <sub>CCPT</sub>      | Power supply for programmable power technology                                                         | _          | 1.45               | 1.50 | 1.55               | V    |

| V <sub>CC_AUX</sub>    | Auxiliary supply for the programmable power technology                                                 | _          | 2.375              | 2.5  | 2.625              | V    |

| V <sub>CCPD</sub> (1)  | I/O pre-driver (3.0 V) power supply                                                                    | _          | 2.85               | 3.0  | 3.15               | V    |

| VCCPD (1)              | I/O pre-driver (2.5 V) power supply                                                                    | _          | 2.375              | 2.5  | 2.625              | V    |

|                        | I/O buffers (3.0 V) power supply                                                                       |            | 2.85               | 3.0  | 3.15               | V    |

|                        | I/O buffers (2.5 V) power supply                                                                       |            | 2.375              | 2.5  | 2.625              | V    |

|                        | I/O buffers (1.8 V) power supply                                                                       | _          | 1.71               | 1.8  | 1.89               | V    |

| V <sub>CCIO</sub>      | I/O buffers (1.5 V) power supply                                                                       |            | 1.425              | 1.5  | 1.575              | V    |

|                        | I/O buffers (1.35 V) power supply                                                                      |            | 1.283              | 1.35 | 1.45               | V    |

|                        | I/O buffers (1.25 V) power supply                                                                      |            | 1.19               | 1.25 | 1.31               | V    |

|                        | I/O buffers (1.2 V) power supply                                                                       | _          | 1.14               | 1.2  | 1.26               | V    |

|                        | Configuration pins (3.0 V) power supply                                                                |            | 2.85               | 3.0  | 3.15               | V    |

| $V_{CCPGM}$            | Configuration pins (2.5 V) power supply                                                                |            | 2.375              | 2.5  | 2.625              | V    |

|                        | Configuration pins (1.8 V) power supply                                                                |            | 1.71               | 1.8  | 1.89               | V    |

| V <sub>CCA_FPLL</sub>  | PLL analog voltage regulator power supply                                                              |            | 2.375              | 2.5  | 2.625              | V    |

| V <sub>CCD_FPLL</sub>  | PLL digital voltage regulator power supply                                                             | _          | 1.45               | 1.5  | 1.55               | V    |

| V <sub>CCBAT</sub> (2) | Battery back-up power supply (For design security volatile key register)                               | _          | 1.2                | _    | 3.0                | V    |

| V <sub>I</sub>         | DC input voltage                                                                                       | _          | -0.5               | _    | 3.6                | V    |

| V <sub>0</sub>         | Output voltage                                                                                         | _          | 0                  | _    | V <sub>CCIO</sub>  | V    |

| т.                     | Operating junction temperature                                                                         | Commercial | 0                  | _    | 85                 | °C   |

| $T_J$                  | Operating junction temperature                                                                         | Industrial | -40                | _    | 100                | °C   |

Page 6 Electrical Characteristics

Table 6. Recommended Operating Conditions for Stratix V Devices (Part 2 of 2)

| Symbol | Description            | Condition    | Min <sup>(4)</sup> | Тур | Max <sup>(4)</sup> | Unit |

|--------|------------------------|--------------|--------------------|-----|--------------------|------|

| +      | Dower cumply rome time | Standard POR | 200 μs             | _   | 100 ms             | _    |

| LRAMP  | Power supply ramp time | Fast POR     | 200 μs             | _   | 4 ms               | _    |

#### Notes to Table 6:

- (1)  $V_{CCPD}$  must be 2.5 V when  $V_{CCIO}$  is 2.5, 1.8, 1.5, 1.35, 1.25 or 1.2 V.  $V_{CCPD}$  must be 3.0 V when  $V_{CCIO}$  is 3.0 V.

- (2) If you do not use the design security feature in Stratix V devices, connect V<sub>CCBAT</sub> to a 1.2- to 3.0-V power supply. Stratix V power-on-reset (POR) circuitry monitors V<sub>CCBAT</sub>. Stratix V devices will not exit POR if V<sub>CCBAT</sub> stays at logic low.

- (3) C2L and I2L can also be run at 0.90 V for legacy boards that were designed for the C2 and I2 speed grades.

- (4) The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

Table 7 lists the transceiver power supply recommended operating conditions for Stratix V GX, GS, and GT devices.

Table 7. Recommended Transceiver Power Supply Operating Conditions for Stratix V GX, GS, and GT Devices (Part 1 of 2)

| Symbol                | Description                                                                                   | Devices    | Minimum (4) | Typical | Maximum <sup>(4)</sup> | Unit |

|-----------------------|-----------------------------------------------------------------------------------------------|------------|-------------|---------|------------------------|------|

| V <sub>CCA_GXBL</sub> | Transceiver channel PLL power supply (left                                                    | GX, GS, GT | 2.85        | 3.0     | 3.15                   | V    |

| (1), (3)              | side)                                                                                         | ux, us, u1 | 2.375       | 2.5     | 2.625                  | V    |

| V <sub>CCA_GXBR</sub> | Transceiver channel PLL power supply (right                                                   | GX, GS     | 2.85        | 3.0     | 3.15                   | V    |

| (1), (3)              | side)                                                                                         | ux, us     | 2.375       | 2.5     | 2.625                  | V    |

| V <sub>CCA_GTBR</sub> | Transceiver channel PLL power supply (right side)                                             | GT         | 2.85        | 3.0     | 3.15                   | V    |

|                       | Transceiver hard IP power supply (left side; C1, C2, I2, and I3YY speed grades)               | GX, GS, GT | 0.87        | 0.9     | 0.93                   | V    |

| V <sub>CCHIP_L</sub>  | Transceiver hard IP power supply (left side; C2L, C3, C4, I2L, I3, I3L, and I4 speed grades)  | GX, GS, GT | 0.82        | 0.85    | 0.88                   | V    |

|                       | Transceiver hard IP power supply (right side; C1, C2, I2, and I3YY speed grades)              | GX, GS, GT | 0.87        | 0.9     | 0.93                   | V    |

| V <sub>CCHIP_R</sub>  | Transceiver hard IP power supply (right side; C2L, C3, C4, I2L, I3, I3L, and I4 speed grades) | GX, GS, GT | 0.82        | 0.85    | 0.88                   | V    |

|                       | Transceiver PCS power supply (left side; C1, C2, I2, and I3YY speed grades)                   | GX, GS, GT | 0.87        | 0.9     | 0.93                   | V    |

| V <sub>CCHSSI_L</sub> | Transceiver PCS power supply (left side; C2L, C3, C4, I2L, I3, I3L, and I4 speed grades)      | GX, GS, GT | 0.82        | 0.85    | 0.88                   | V    |

|                       | Transceiver PCS power supply (right side; C1, C2, I2, and I3YY speed grades)                  | GX, GS, GT | 0.87        | 0.9     | 0.93                   | V    |

| V <sub>CCHSSI_R</sub> | Transceiver PCS power supply (right side; C2L, C3, C4, I2L, I3, I3L, and I4 speed grades)     | GX, GS, GT | 0.82        | 0.85    | 0.88                   | V    |

|                       |                                                                                               |            | 0.82        | 0.85    | 0.88                   |      |

| V <sub>CCR_GXBL</sub> | Pagaiyar analog nawar ayanlı (laft aida)                                                      | CV CC CT   | 0.87        | 0.90    | 0.93                   | V    |

| (2)                   | Receiver analog power supply (left side)                                                      | GX, GS, GT | 0.97        | 1.0     | 1.03                   | V    |

|                       |                                                                                               |            | 1.03        | 1.05    | 1.07                   |      |

Table 7. Recommended Transceiver Power Supply Operating Conditions for Stratix V GX, GS, and GT Devices (Part 2 of 2)

| Symbol                | Description                                                  | Devices    | Minimum (4) | Typical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Maximum (4)                                                                                                   | Unit |

|-----------------------|--------------------------------------------------------------|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|

|                       |                                                              |            | 0.82        | 0.85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.88                                                                                                          |      |

| V <sub>CCR_GXBR</sub> | Pagaiyar analog nawar ayanly (right aida)                    | GX, GS, GT | 0.87        | 0.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.93                                                                                                          | W    |

| (2)                   | Receiver analog power supply (right side)                    |            | 0.97        | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.03                                                                                                          | V    |

|                       |                                                              |            | 1.03        | 0.82       0.85       0.88         0.87       0.90       0.93         0.97       1.0       1.03         1.03       1.05       1.07         1.02       1.05       1.08         0.82       0.85       0.88         0.87       0.90       0.93         0.97       1.0       1.03         1.03       1.05       1.07         0.82       0.85       0.88         0.87       0.90       0.93         0.97       1.0       1.03         1.03       1.05       1.07         1.03       1.05       1.07         1.02       1.05       1.08       V         1.02       1.05       1.08       V         1.425       1.5       1.575       V |                                                                                                               |      |

| V <sub>CCR_GTBR</sub> | Receiver analog power supply for GT channels (right side)    | GT         | 1.02        | 1.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.08                                                                                                          | V    |

|                       |                                                              |            | 0.82        | 0.85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.88                                                                                                          |      |

| V <sub>CCT_GXBL</sub> | Transmitter analog power supply (left side)                  | GX, GS, GT | 0.87        | 0.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.93                                                                                                          | V    |

|                       |                                                              |            | 0.97        | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.03                                                                                                          |      |

|                       |                                                              |            | 1.03        | 1.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.03<br>1.07<br>0.88<br>0.93                                                                                  |      |

|                       |                                                              | GX, GS, GT | 0.82        | 0.85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.88                                                                                                          | V    |

| V <sub>CCT_GXBR</sub> | Transmitter analog power supply (right side)                 |            | 0.87        | 0.90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0.93                                                                                                          |      |

| (2)                   | Transmitter analog power supply (right side)                 |            | 0.97        | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.03                                                                                                          |      |

|                       |                                                              |            | 1.03        | 1.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.03<br>1.07<br>1.08<br>0.88<br>0.93<br>1.03<br>1.07<br>0.88<br>0.93<br>1.03<br>1.07<br>1.08<br>1.08<br>1.575 |      |

| V <sub>CCT_GTBR</sub> | Transmitter analog power supply for GT channels (right side) | GT         | 1.02        | 1.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.08                                                                                                          | V    |

| V <sub>CCL_GTBR</sub> | Transmitter clock network power supply                       | GT         | 1.02        | 1.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.08                                                                                                          | V    |

| V <sub>CCH_GXBL</sub> | Transmitter output buffer power supply (left side)           | GX, GS, GT | 1.425       | 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.575                                                                                                         | V    |

| V <sub>CCH_GXBR</sub> | Transmitter output buffer power supply (right side)          | GX, GS, GT | 1.425       | 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.575                                                                                                         | V    |

#### Notes to Table 7:

<sup>(1)</sup> This supply must be connected to 3.0 V if the CMU PLL, receiver CDR, or both, are configured at a base data rate > 6.5 Gbps. Up to 6.5 Gbps, you can connect this supply to either 3.0 V or 2.5 V.

<sup>(2)</sup> Refer to Table 8 to select the correct power supply level for your design.

<sup>(3)</sup> When using ATX PLLs, the supply must be 3.0 V.

<sup>(4)</sup> This value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

Page 8 Electrical Characteristics

Table 8 shows the transceiver power supply voltage requirements for various conditions.

**Table 8. Transceiver Power Supply Voltage Requirements**

| Conditions                                                         | Core Speed Grade                  | VCCR_GXB & VCCT_GXB (2) | VCCA_GXB | VCCH_GXB | Unit |

|--------------------------------------------------------------------|-----------------------------------|-------------------------|----------|----------|------|

| If BOTH of the following conditions are true:                      |                                   | 4.05                    |          |          |      |

| ■ Data rate > 10.3 Gbps.                                           | All                               | 1.05                    |          |          |      |

| DFE is used.                                                       |                                   |                         |          |          |      |

| If ANY of the following conditions are true (1):                   |                                   |                         | 3.0      |          |      |

| ATX PLL is used.                                                   |                                   |                         |          |          |      |

| ■ Data rate > 6.5Gbps.                                             | All                               | 1.0                     |          |          |      |

| ■ DFE (data rate ≤<br>10.3 Gbps), AEQ, or<br>EyeQ feature is used. |                                   |                         |          | 1.5      | V    |

| If ALL of the following                                            | C1, C2, I2, and I3YY              | 0.90                    | 2.5      |          |      |

| conditions are true:  ATX PLL is not used.                         |                                   |                         |          |          |      |

| ■ Data rate ≤ 6.5Gbps.                                             | C2L, C3, C4, I2L, I3, I3L, and I4 | 0.85                    | 2.5      |          |      |

| DFE, AEQ, and EyeQ are<br>not used.                                |                                   |                         |          |          |      |

#### Notes to Table 8:

- (1) Choose this power supply voltage requirement option if you plan to upgrade your design later with any of the listed conditions.

- (2) If the VCCR\_GXB and VCCT\_GXB supplies are set to 1.0 V or 1.05 V, they cannot be shared with the VCC core supply. If the VCCR\_GXB and VCCT\_GXB are set to either 0.90 V or 0.85 V, they can be shared with the VCC core supply.

## **DC Characteristics**

This section lists the supply current, I/O pin leakage current, input pin capacitance, on-chip termination tolerance, and hot socketing specifications.

## **Supply Current**

Supply current is the current drawn from the respective power rails used for power budgeting. Use the Excel-based Early Power Estimator (EPE) to get supply current estimates for your design because these currents vary greatly with the resources you use.

For more information about power estimation tools, refer to the *PowerPlay Early Power Estimator User Guide* and the *PowerPlay Power Analysis* chapter in the *Quartus II Handbook*.

# I/O Pin Leakage Current

Table 9 lists the Stratix V I/O pin leakage current specifications.

Table 9. I/O Pin Leakage Current for Stratix V Devices (1)

| Symbol          | Description        | Conditions                                 | Min | Тур | Max | Unit |

|-----------------|--------------------|--------------------------------------------|-----|-----|-----|------|

| I               | Input pin          | $V_I = 0 V \text{ to } V_{CCIOMAX}$        | -30 | _   | 30  | μΑ   |

| I <sub>OZ</sub> | Tri-stated I/O pin | $V_0 = 0 V \text{ to } V_{\text{CCIOMAX}}$ | -30 | _   | 30  | μΑ   |

#### Note to Table 9:

(1) If  $V_0$  =  $V_{CCIO}$  to  $V_{CCIOMax}$ , 100  $\mu A$  of leakage current per I/O is expected.

## **Bus Hold Specifications**

Table 10 lists the Stratix V device family bus hold specifications.

Table 10. Bus Hold Parameters for Stratix V Devices

|                               |                   | ymbol Conditions                               |       |      |       |       | V     | CCIO |       |      |       |      |      |

|-------------------------------|-------------------|------------------------------------------------|-------|------|-------|-------|-------|------|-------|------|-------|------|------|

| Parameter                     | Symbol            |                                                | 1.2 V |      | 1.9   | 1.5 V |       | B V  | 2.5 V |      | 3.0 V |      | Unit |

|                               |                   |                                                | Min   | Max  | Min   | Max   | Min   | Max  | Min   | Max  | Min   | Max  |      |

| Low<br>sustaining<br>current  | I <sub>SUSL</sub> | V <sub>IN</sub> > V <sub>IL</sub><br>(maximum) | 22.5  | _    | 25.0  | _     | 30.0  | _    | 50.0  | _    | 70.0  | _    | μА   |

| High<br>sustaining<br>current | I <sub>SUSH</sub> | V <sub>IN</sub> < V <sub>IH</sub><br>(minimum) | -22.5 | _    | -25.0 | _     | -30.0 | _    | -50.0 | _    | -70.0 | _    | μА   |

| Low<br>overdrive<br>current   | I <sub>ODL</sub>  | 0V < V <sub>IN</sub> < V <sub>CCIO</sub>       | _     | 120  |       | 160   |       | 200  |       | 300  | _     | 500  | μА   |

| High<br>overdrive<br>current  | I <sub>ODH</sub>  | 0V < V <sub>IN</sub> < V <sub>CCIO</sub>       | _     | -120 | —     | -160  | _     | -200 |       | -300 | _     | -500 | μА   |

| Bus-hold<br>trip point        | V <sub>TRIP</sub> | _                                              | 0.45  | 0.95 | 0.50  | 1.00  | 0.68  | 1.07 | 0.70  | 1.70 | 0.80  | 2.00 | V    |

# **On-Chip Termination (OCT) Specifications**

If you enable OCT calibration, calibration is automatically performed at power-up for I/Os connected to the calibration block. Table 11 lists the Stratix V OCT termination calibration accuracy specifications.

Table 11. OCT Calibration Accuracy Specifications for Stratix V Devices (1) (Part 1 of 2)

| Symbol              |                                                                     |                                                  | Calibration Accuracy |       |                |       |      |

|---------------------|---------------------------------------------------------------------|--------------------------------------------------|----------------------|-------|----------------|-------|------|

|                     | Description                                                         | Conditions                                       | C1                   | C2,I2 | C3,I3,<br>I3YY | C4,I4 | Unit |

| 25-Ω R <sub>S</sub> | Internal series termination with calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 3.0, 2.5,<br>1.8, 1.5, 1.2 V | ±15                  | ±15   | ±15            | ±15   | %    |

Page 10 Electrical Characteristics

Table 11. OCT Calibration Accuracy Specifications for Stratix V Devices (1) (Part 2 of 2)

|                                                                                                                                            | ,                                                                                                                                      |                                                  | 1          |            |                |            |      |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------|------------|----------------|------------|------|

|                                                                                                                                            |                                                                                                                                        |                                                  |            | Calibratio | n Accuracy     |            |      |

| Symbol                                                                                                                                     | Description                                                                                                                            | Conditions                                       | C1         | C2,I2      | C3,I3,<br>I3YY | C4,I4      | Unit |

| 50-Ω R <sub>S</sub>                                                                                                                        | Internal series termination with calibration (50- $\Omega$ setting)                                                                    | V <sub>CCIO</sub> = 3.0, 2.5,<br>1.8, 1.5, 1.2 V | ±15        | ±15        | ±15            | ±15        | %    |

| $34\text{-}\Omega$ and $40\text{-}\Omega$ $R_S$                                                                                            | Internal series termination with calibration (34- $\Omega$ and 40- $\Omega$ setting)                                                   | V <sub>CCIO</sub> = 1.5, 1.35,<br>1.25, 1.2 V    | ±15        | ±15        | ±15            | ±15        | %    |

| $48$ - $\Omega$ , $60$ - $\Omega$ , $80$ - $\Omega$ , and $240$ - $\Omega$ R <sub>S</sub>                                                  | Internal series termination with calibration (48- $\Omega$ , 60- $\Omega$ , 80- $\Omega$ , and 240- $\Omega$ setting)                  | V <sub>CCIO</sub> = 1.2 V                        | ±15        | ±15        | ±15            | ±15        | %    |

| 50-Ω R <sub>T</sub>                                                                                                                        | Internal parallel termination with calibration (50-Ω setting)                                                                          | V <sub>CCIO</sub> = 2.5, 1.8,<br>1.5, 1.2 V      | -10 to +40 | -10 to +40 | -10 to +40     | -10 to +40 | %    |

| $\begin{array}{c} 20\text{-}\Omega,30\text{-}\Omega,\\ 40\text{-}\Omega,60\text{-}\Omega,\\ \text{and}\\ 120\text{-}\OmegaR_T \end{array}$ | Internal parallel termination with calibration (20- $\Omega$ , 30- $\Omega$ , 40- $\Omega$ , 60- $\Omega$ , and 120- $\Omega$ setting) | V <sub>CCIO</sub> = 1.5, 1.35,<br>1.25 V         | -10 to +40 | -10 to +40 | -10 to +40     | -10 to +40 | %    |

| 60- $\Omega$ and 120- $\Omega$ R <sub>T</sub>                                                                                              | Internal parallel termination with calibration (60- $\Omega$ and 120- $\Omega$ setting)                                                | V <sub>CCIO</sub> = 1.2                          | -10 to +40 | -10 to +40 | -10 to +40     | -10 to +40 | %    |

| $\begin{array}{c} \textbf{25-}\Omega \\ \textbf{R}_{S\_left\_shift} \end{array}$                                                           | Internal left shift series termination with calibration (25- $\Omega$ $R_{S\_left\_shift}$ setting)                                    | V <sub>CCIO</sub> = 3.0, 2.5,<br>1.8, 1.5, 1.2 V | ±15        | ±15        | ±15            | ±15        | %    |

## Note to Table 11:

Table 12 lists the Stratix V OCT without calibration resistance tolerance to PVT changes.

Table 12. OCT Without Calibration Resistance Tolerance Specifications for Stratix V Devices (Part 1 of 2)

|                             |                                                                        |                                   | Resistance Tolerance |       |                 |        |      |

|-----------------------------|------------------------------------------------------------------------|-----------------------------------|----------------------|-------|-----------------|--------|------|

| Symbol                      | Description                                                            | Conditions                        | <b>C</b> 1           | C2,I2 | C3, I3,<br>I3YY | C4, I4 | Unit |

| 25-Ω R, 50-Ω R <sub>S</sub> | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CC10</sub> = 3.0 and 2.5 V | ±30                  | ±30   | ±40             | ±40    | %    |

| 25-Ω R <sub>S</sub>         | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CC10</sub> = 1.8 and 1.5 V | ±30                  | ±30   | ±40             | ±40    | %    |

| 25-Ω R <sub>S</sub>         | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 1.2 V         | ±35                  | ±35   | ±50             | ±50    | %    |

$<sup>\</sup>hbox{ (1)} \quad \hbox{OCT calibration accuracy is valid at the time of calibration only.}$

Table 12. OCT Without Calibration Resistance Tolerance Specifications for Stratix V Devices (Part 2 of 2)

|                      |                                                                        |                                   | Resistance Tolerance |       |                 |        |      |

|----------------------|------------------------------------------------------------------------|-----------------------------------|----------------------|-------|-----------------|--------|------|

| Symbol               | Description                                                            | Conditions                        | C1                   | C2,I2 | C3, I3,<br>I3YY | C4, I4 | Unit |

| 50-Ω R <sub>S</sub>  | Internal series termination without calibration (50- $\Omega$ setting) | V <sub>CCIO</sub> = 1.8 and 1.5 V | ±30                  | ±30   | ±40             | ±40    | %    |

| 50-Ω R <sub>S</sub>  | Internal series termination without calibration (50- $\Omega$ setting) | V <sub>CCIO</sub> = 1.2 V         | ±35                  | ±35   | ±50             | ±50    | %    |

| 100-Ω R <sub>D</sub> | Internal differential termination (100-Ω setting)                      | V <sub>CCPD</sub> = 2.5 V         | ±25                  | ±25   | ±25             | ±25    | %    |

Calibration accuracy for the calibrated series and parallel OCTs are applicable at the moment of calibration. When voltage and temperature conditions change after calibration, the tolerance may change.

OCT calibration is automatically performed at power-up for OCT-enabled I/Os. Table 13 lists the OCT variation with temperature and voltage after power-up calibration. Use Table 13 to determine the OCT variation after power-up calibration and Equation 1 to determine the OCT variation without recalibration.

Equation 1. OCT Variation Without Recalibration for Stratix V Devices (1), (2), (3), (4), (5), (6)

$$R_{OCT} = R_{SCAL} \Big( 1 + \langle \frac{dR}{dT} \times \Delta T \rangle \pm \langle \frac{dR}{dV} \times \Delta V \rangle \Big)$$

## Notes to Equation 1:

- (1) The  $R_{OCT}$  value shows the range of OCT resistance with the variation of temperature and  $V_{CCIO}$ .

- (2) R<sub>SCAL</sub> is the OCT resistance value at power-up.

- (3)  $\Delta T$  is the variation of temperature with respect to the temperature at power-up.

- (4)  $\Delta V$  is the variation of voltage with respect to the  $V_{CCIO}$  at power-up.

- (5) dR/dT is the percentage change of  $R_{\text{SCAL}}$  with temperature.

- (6) dR/dV is the percentage change of  $R_{SCAL}$  with voltage.

Table 13 lists the on-chip termination variation after power-up calibration.

Table 13. OCT Variation after Power-Up Calibration for Stratix V Devices (Part 1 of 2) (1)

| Symbol | Description                                      | V <sub>CCIO</sub> (V) | Typical | Unit |

|--------|--------------------------------------------------|-----------------------|---------|------|

| dR/dV  |                                                  | 3.0                   | 0.0297  |      |

|        | OCT variation with voltage without recalibration | 2.5                   | 0.0344  | %/mV |

|        |                                                  | 1.8                   | 0.0499  |      |

|        | Todalistation                                    | 1.5                   | 0.0744  |      |

|        |                                                  | 1.2                   | 0.1241  |      |

Page 12 Electrical Characteristics

Table 13. OCT Variation after Power-Up Calibration for Stratix V Devices (Part 2 of 2) (1)

| Symbol | Description                                          | V <sub>CCIO</sub> (V) | Typical | Unit |  |

|--------|------------------------------------------------------|-----------------------|---------|------|--|

|        |                                                      | 3.0                   | 0.189   |      |  |

|        | 007                                                  | 2.5                   | 0.208   | %/°C |  |

| dR/dT  | OCT variation with temperature without recalibration | 1.8                   | 0.266   |      |  |

|        | William ToodiisTation                                | 1.5                   | 0.273   |      |  |

|        |                                                      | 1.2                   | 0.317   |      |  |

#### Note to Table 13:

(1) Valid for a  $V_{\text{CCIO}}$  range of  $\pm 5\%$  and a temperature range of 0° to 85°C.

# **Pin Capacitance**

Table 14 lists the Stratix V device family pin capacitance.

**Table 14. Pin Capacitance for Stratix V Devices**

| Symbol             | Description                                                      | Value | Unit |

|--------------------|------------------------------------------------------------------|-------|------|

| C <sub>IOTB</sub>  | Input capacitance on the top and bottom I/O pins                 | 6     | pF   |

| C <sub>IOLR</sub>  | Input capacitance on the left and right I/O pins                 | 6     | pF   |

| C <sub>OUTFB</sub> | Input capacitance on dual-purpose clock output and feedback pins | 6     | pF   |

## **Hot Socketing**

Table 15 lists the hot socketing specifications for Stratix V devices.

Table 15. Hot Socketing Specifications for Stratix V Devices

| Symbol                    | Description                                | Maximum             |

|---------------------------|--------------------------------------------|---------------------|

| I <sub>IOPIN (DC)</sub>   | DC current per I/O pin                     | 300 μΑ              |

| I <sub>IOPIN (AC)</sub>   | AC current per I/O pin                     | 8 mA <sup>(1)</sup> |

| I <sub>XCVR-TX (DC)</sub> | DC current per transceiver transmitter pin | 100 mA              |

| I <sub>XCVR-RX (DC)</sub> | DC current per transceiver receiver pin    | 50 mA               |

#### Note to Table 15:

(1) The I/O ramp rate is 10 ns or more. For ramp rates faster than 10 ns,  $|I_{IOPIN}| = C dv/dt$ , in which C is the I/O pin capacitance and dv/dt is the slew rate.

# **Internal Weak Pull-Up Resistor**

Table 16 lists the weak pull-up resistor values for Stratix V devices.

Table 16. Internal Weak Pull-Up Resistor for Stratix V Devices (1), (2)

| Symbol          | Description                                                                   | V <sub>CC10</sub> Conditions<br>(V) <sup>(3)</sup> | Value <sup>(4)</sup> | Unit |  |

|-----------------|-------------------------------------------------------------------------------|----------------------------------------------------|----------------------|------|--|

|                 |                                                                               | 3.0 ±5%                                            | 25                   | kΩ   |  |

|                 |                                                                               | 2.5 ±5%                                            |                      |      |  |

|                 | Value of the I/O pin pull-up resistor before                                  | 1.8 ±5%                                            | 25                   | kΩ   |  |

| R <sub>PU</sub> | and during configuration, as well as user mode if you enable the programmable | 1.5 ±5%                                            | 25                   | kΩ   |  |

|                 | pull-up resistor option.                                                      | 1.35 ±5%                                           | 25                   | kΩ   |  |

|                 |                                                                               | 1.25 ±5%                                           | 25                   | kΩ   |  |

|                 |                                                                               | 1.2 ±5%                                            | 25                   | kΩ   |  |

#### Notes to Table 16:

- (1) All I/O pins have an option to enable the weak pull-up resistor except the configuration, test, and JTAG pins.

- (2) The internal weak pull-down feature is only available for the JTAG TCK pin. The typical value for this internal weak pull-down resistor is approximately 25 k $\Omega$ .

- (3) The pin pull-up resistance values may be lower if an external source drives the pin higher than  $V_{CCIO}$ .

- (4) These specifications are valid with a ±10% tolerance to cover changes over PVT.

# I/O Standard Specifications

Table 17 through Table 22 list the input voltage ( $V_{IH}$  and  $V_{IL}$ ), output voltage ( $V_{OH}$  and  $V_{OL}$ ), and current drive characteristics ( $I_{OH}$  and  $I_{OL}$ ) for various I/O standards supported by Stratix V devices. These tables also show the Stratix V device family I/O standard specifications. The  $V_{OL}$  and  $V_{OH}$  values are valid at the corresponding  $I_{OH}$  and  $I_{OL}$ , respectively.

For an explanation of the terms used in Table 17 through Table 22, refer to "Glossary" on page 66. For tolerance calculations across all SSTL and HSTL I/O standards, refer to Altera knowledge base solution rd07262012\_486.

Table 17. Single-Ended I/O Standards for Stratix V Devices

| 1/0      |       | V <sub>CCIO</sub> (V) |       | V <sub>IL</sub> (V) |                             | V <sub>IH</sub>             | (V)                     | V <sub>OL</sub> (V)         | V <sub>OH</sub> (V)         | I <sub>OL</sub> | I <sub>OH</sub> |

|----------|-------|-----------------------|-------|---------------------|-----------------------------|-----------------------------|-------------------------|-----------------------------|-----------------------------|-----------------|-----------------|

| Standard | Min   | Тур                   | Max   | Min                 | Max                         | Min                         | Max                     | Max                         | Min                         | (mĀ)            | (mA)            |

| LVTTL    | 2.85  | 3                     | 3.15  | -0.3                | 0.8                         | 1.7                         | 3.6                     | 0.4                         | 2.4                         | 2               | -2              |

| LVCMOS   | 2.85  | 3                     | 3.15  | -0.3                | 0.8                         | 1.7                         | 3.6                     | 0.2                         | V <sub>CCIO</sub> - 0.2     | 0.1             | -0.1            |

| 2.5 V    | 2.375 | 2.5                   | 2.625 | -0.3                | 0.7                         | 1.7                         | 3.6                     | 0.4                         | 2                           | 1               | -1              |

| 1.8 V    | 1.71  | 1.8                   | 1.89  | -0.3                | 0.35 *<br>V <sub>CCIO</sub> | 0.65 *<br>V <sub>CCIO</sub> | V <sub>CCIO</sub> + 0.3 | 0.45                        | V <sub>CCIO</sub> –<br>0.45 | 2               | -2              |

| 1.5 V    | 1.425 | 1.5                   | 1.575 | -0.3                | 0.35 *<br>V <sub>CCIO</sub> | 0.65 *<br>V <sub>CCIO</sub> | V <sub>CCIO</sub> + 0.3 | 0.25 *<br>V <sub>CCIO</sub> | 0.75 *<br>V <sub>CCIO</sub> | 2               | -2              |

| 1.2 V    | 1.14  | 1.2                   | 1.26  | -0.3                | 0.35 *<br>V <sub>CCIO</sub> | 0.65 *<br>V <sub>CCIO</sub> | V <sub>CCIO</sub> + 0.3 | 0.25 *<br>V <sub>CCIO</sub> | 0.75 *<br>V <sub>CCIO</sub> | 2               | -2              |

Page 14 Electrical Characteristics

Table 18. Single-Ended SSTL, HSTL, and HSUL I/O Reference Voltage Specifications for Stratix V Devices

| I/O Standard            |       | V <sub>CCIO</sub> (V) |       |                             | V <sub>REF</sub> (V)    |                             |                             | V <sub>TT</sub> (V)        |                             |

|-------------------------|-------|-----------------------|-------|-----------------------------|-------------------------|-----------------------------|-----------------------------|----------------------------|-----------------------------|

| I/O Standard            | Min   | Тур                   | Max   | Min                         | Тур                     | Max                         | Min                         | Тур                        | Мах                         |

| SSTL-2<br>Class I, II   | 2.375 | 2.5                   | 2.625 | 0.49 *<br>V <sub>CCIO</sub> | 0.5 * V <sub>CCIO</sub> | 0.51 *<br>V <sub>CCIO</sub> | V <sub>REF</sub> –<br>0.04  | $V_{REF}$                  | V <sub>REF</sub> + 0.04     |

| SSTL-18<br>Class I, II  | 1.71  | 1.8                   | 1.89  | 0.833                       | 0.9                     | 0.969                       | V <sub>REF</sub> – 0.04     | $V_{REF}$                  | V <sub>REF</sub> + 0.04     |

| SSTL-15<br>Class I, II  | 1.425 | 1.5                   | 1.575 | 0.49 *<br>V <sub>CCIO</sub> | 0.5 * V <sub>CCIO</sub> | 0.51 *<br>V <sub>CCIO</sub> | 0.49 *<br>V <sub>CCIO</sub> | 0.5 *<br>VCCIO             | 0.51 *<br>V <sub>CCIO</sub> |

| SSTL-135<br>Class I, II | 1.283 | 1.35                  | 1.418 | 0.49 *<br>V <sub>CCIO</sub> | 0.5 * V <sub>CCIO</sub> | 0.51 *<br>V <sub>CCIO</sub> | 0.49 *<br>V <sub>CCIO</sub> | 0.5 *<br>V <sub>CCIO</sub> | 0.51 *<br>V <sub>CCIO</sub> |

| SSTL-125<br>Class I, II | 1.19  | 1.25                  | 1.26  | 0.49 *<br>V <sub>CCIO</sub> | 0.5 * V <sub>CCIO</sub> | 0.51 *<br>V <sub>CCIO</sub> | 0.49 *<br>V <sub>CCIO</sub> | 0.5 *<br>VCCIO             | 0.51 *<br>V <sub>CCIO</sub> |

| SSTL-12<br>Class I, II  | 1.14  | 1.20                  | 1.26  | 0.49 *<br>V <sub>CCIO</sub> | 0.5 * V <sub>CCIO</sub> | 0.51 *<br>V <sub>CCIO</sub> | 0.49 *<br>V <sub>CCIO</sub> | 0.5 *<br>VCCIO             | 0.51 *<br>V <sub>CCIO</sub> |

| HSTL-18<br>Class I, II  | 1.71  | 1.8                   | 1.89  | 0.85                        | 0.9                     | 0.95                        | _                           | V <sub>CCIO</sub> /2       | _                           |

| HSTL-15<br>Class I, II  | 1.425 | 1.5                   | 1.575 | 0.68                        | 0.75                    | 0.9                         | _                           | V <sub>CCIO</sub> /2       | _                           |

| HSTL-12<br>Class I, II  | 1.14  | 1.2                   | 1.26  | 0.47 *<br>V <sub>CCIO</sub> | 0.5 * V <sub>CCIO</sub> | 0.53 *<br>V <sub>CCIO</sub> | _                           | V <sub>CCIO</sub> /2       | _                           |

| HSUL-12                 | 1.14  | 1.2                   | 1.3   | 0.49 *<br>V <sub>CCIO</sub> | 0.5 * V <sub>CCIO</sub> | 0.51 *<br>V <sub>CCIO</sub> | _                           | _                          | _                           |

Table 19. Single-Ended SSTL, HSTL, and HSUL I/O Standards Signal Specifications for Stratix V Devices (Part 1 of 2)

| Table 15: Onle          | ,                  |                          | -,                       | ,                       |                            | - гросиновино            |                            |                            | , t- m-t             | · · · -,        |

|-------------------------|--------------------|--------------------------|--------------------------|-------------------------|----------------------------|--------------------------|----------------------------|----------------------------|----------------------|-----------------|

| I/O Standard            | V <sub>IL(D(</sub> | <sub>C)</sub> (V)        | V <sub>IH(D</sub>        | <sub>C)</sub> (V)       | V <sub>IL(AC)</sub> (V)    | V <sub>IH(AC)</sub> (V)  | V <sub>OL</sub> (V)        | V <sub>OH</sub> (V)        | I (m/\)              | l <sub>oh</sub> |

| i/U Stanuaru            | Min                | Max                      | Min                      | Max                     | Max                        | Min                      | Max                        | Min                        | I <sub>ol</sub> (mA) | (mA)            |

| SSTL-2<br>Class I       | -0.3               | V <sub>REF</sub> – 0.15  | V <sub>REF</sub> + 0.15  | V <sub>CCIO</sub> + 0.3 | V <sub>REF</sub> –<br>0.31 | V <sub>REF</sub> + 0.31  | V <sub>TT</sub> – 0.608    | V <sub>TT</sub> + 0.608    | 8.1                  | -8.1            |

| SSTL-2<br>Class II      | -0.3               | V <sub>REF</sub> – 0.15  | V <sub>REF</sub> + 0.15  | V <sub>CCIO</sub> + 0.3 | V <sub>REF</sub> – 0.31    | V <sub>REF</sub> + 0.31  | V <sub>TT</sub> – 0.81     | V <sub>TT</sub> + 0.81     | 16.2                 | -16.2           |

| SSTL-18<br>Class I      | -0.3               | V <sub>REF</sub> – 0.125 | V <sub>REF</sub> + 0.125 | V <sub>CCIO</sub> + 0.3 | V <sub>REF</sub> – 0.25    | V <sub>REF</sub> + 0.25  | V <sub>TT</sub> – 0.603    | V <sub>TT</sub> + 0.603    | 6.7                  | -6.7            |

| SSTL-18<br>Class II     | -0.3               | V <sub>REF</sub> – 0.125 | V <sub>REF</sub> + 0.125 | V <sub>CCIO</sub> + 0.3 | V <sub>REF</sub> –<br>0.25 | V <sub>REF</sub> + 0.25  | 0.28                       | V <sub>CCIO</sub> - 0.28   | 13.4                 | -13.4           |

| SSTL-15<br>Class I      | _                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | _                       | V <sub>REF</sub> – 0.175   | V <sub>REF</sub> + 0.175 | 0.2 *<br>V <sub>CCIO</sub> | 0.8 *<br>V <sub>CCIO</sub> | 8                    | -8              |

| SSTL-15<br>Class II     | _                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | _                       | V <sub>REF</sub> – 0.175   | V <sub>REF</sub> + 0.175 | 0.2 *<br>V <sub>CCIO</sub> | 0.8 *<br>V <sub>CCIO</sub> | 16                   | -16             |

| SSTL-135<br>Class I, II | _                  | V <sub>REF</sub> – 0.09  | V <sub>REF</sub> + 0.09  | _                       | V <sub>REF</sub> –<br>0.16 | V <sub>REF</sub> + 0.16  | 0.2 *<br>V <sub>CCIO</sub> | 0.8 *<br>V <sub>CCIO</sub> | _                    | _               |

| SSTL-125<br>Class I, II | _                  | V <sub>REF</sub> – 0.85  | V <sub>REF</sub> + 0.85  | _                       | V <sub>REF</sub> –<br>0.15 | V <sub>REF</sub> + 0.15  | 0.2 *<br>V <sub>CCIO</sub> | 0.8 *<br>V <sub>CCIO</sub> | _                    | _               |

| SSTL-12<br>Class I, II  | _                  | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1   | _                       | V <sub>REF</sub> –<br>0.15 | V <sub>REF</sub> + 0.15  | 0.2 *<br>V <sub>CCIO</sub> | 0.8 *<br>V <sub>CCIO</sub> | _                    | _               |

Table 19. Single-Ended SSTL, HSTL, and HSUL I/O Standards Signal Specifications for Stratix V Devices (Part 2 of 2)

|                     | T                  |                         |                         |                          |                            |                         |                            |                            |                        |                 |

|---------------------|--------------------|-------------------------|-------------------------|--------------------------|----------------------------|-------------------------|----------------------------|----------------------------|------------------------|-----------------|

| I/O Standard        | V <sub>IL(D(</sub> | <sub>:)</sub> (V)       | V <sub>IH(D</sub>       | <sub>C)</sub> (V)        | V <sub>IL(AC)</sub> (V)    | V <sub>IH(AC)</sub> (V) | V <sub>OL</sub> (V)        | V <sub>OH</sub> (V)        | I <sub>ol</sub> (mA)   | l <sub>oh</sub> |

| i/o Stanuaru        | Min                | Max                     | Min                     | Max                      | Max                        | Min                     | Max                        | Min                        | I <sub>OI</sub> (IIIA) | (mA)            |

| HSTL-18<br>Class I  | _                  | V <sub>REF</sub> – 0.1  | V <sub>REF</sub> + 0.1  | _                        | V <sub>REF</sub> – 0.2     | V <sub>REF</sub> + 0.2  | 0.4                        | V <sub>CCIO</sub> – 0.4    | 8                      | -8              |

| HSTL-18<br>Class II | _                  | V <sub>REF</sub> – 0.1  | V <sub>REF</sub> + 0.1  | _                        | V <sub>REF</sub> - 0.2     | V <sub>REF</sub> + 0.2  | 0.4                        | V <sub>CCIO</sub> – 0.4    | 16                     | -16             |

| HSTL-15<br>Class I  | _                  | V <sub>REF</sub> – 0.1  | V <sub>REF</sub> + 0.1  | _                        | V <sub>REF</sub> - 0.2     | V <sub>REF</sub> + 0.2  | 0.4                        | V <sub>CCIO</sub> – 0.4    | 8                      | -8              |

| HSTL-15<br>Class II | _                  | V <sub>REF</sub> – 0.1  | V <sub>REF</sub> + 0.1  | _                        | V <sub>REF</sub> - 0.2     | V <sub>REF</sub> + 0.2  | 0.4                        | V <sub>CCIO</sub> – 0.4    | 16                     | -16             |

| HSTL-12<br>Class I  | -0.15              | V <sub>REF</sub> – 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15 | V <sub>REF</sub> –<br>0.15 | V <sub>REF</sub> + 0.15 | 0.25*<br>V <sub>CCIO</sub> | 0.75*<br>V <sub>CCIO</sub> | 8                      | -8              |

| HSTL-12<br>Class II | -0.15              | V <sub>REF</sub> – 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15 | V <sub>REF</sub> –<br>0.15 | V <sub>REF</sub> + 0.15 | 0.25*<br>V <sub>CCIO</sub> | 0.75*<br>V <sub>CCIO</sub> | 16                     | -16             |

| HSUL-12             | _                  | V <sub>REF</sub> – 0.13 | V <sub>REF</sub> + 0.13 | _                        | V <sub>REF</sub> –<br>0.22 | V <sub>REF</sub> + 0.22 | 0.1*<br>V <sub>CCIO</sub>  | 0.9*<br>V <sub>CCIO</sub>  | _                      | _               |

Table 20. Differential SSTL I/O Standards for Stratix V Devices

| I/O Standard            |       | V <sub>CCIO</sub> (V) |       | V <sub>SWIN</sub> | <sub>G(DC)</sub> (V)    |                              | V <sub>X(AC)</sub> (V) |                              | V <sub>SWING(</sub>                        | <sub>AC)</sub> (V)                            |

|-------------------------|-------|-----------------------|-------|-------------------|-------------------------|------------------------------|------------------------|------------------------------|--------------------------------------------|-----------------------------------------------|

| I/O Standard            | Min   | Тур                   | Max   | Min               | Max                     | Min                          | Тур                    | Max                          | Min                                        | Max                                           |

| SSTL-2 Class<br>I, II   | 2.375 | 2.5                   | 2.625 | 0.3               | V <sub>CCIO</sub> + 0.6 | V <sub>CCIO</sub> /2 – 0.2   | _                      | V <sub>CCIO</sub> /2 + 0.2   | 0.62                                       | V <sub>CCIO</sub> + 0.6                       |

| SSTL-18 Class<br>I, II  | 1.71  | 1.8                   | 1.89  | 0.25              | V <sub>CCIO</sub> + 0.6 | V <sub>CCIO</sub> /2 – 0.175 | _                      | V <sub>CCIO</sub> /2 + 0.175 | 0.5                                        | V <sub>CCIO</sub> + 0.6                       |

| SSTL-15 Class<br>I, II  | 1.425 | 1.5                   | 1.575 | 0.2               | (1)                     | V <sub>CCIO</sub> /2 – 0.15  | _                      | V <sub>CCIO</sub> /2 + 0.15  | 0.35                                       | _                                             |

| SSTL-135<br>Class I, II | 1.283 | 1.35                  | 1.45  | 0.2               | (1)                     | V <sub>CCIO</sub> /2 – 0.15  | V <sub>CCIO</sub> /2   | V <sub>CCIO</sub> /2 + 0.15  | 2(V <sub>IH(AC)</sub> - V <sub>REF</sub> ) | 2(V <sub>IL(AC)</sub><br>- V <sub>REF</sub> ) |

| SSTL-125<br>Class I, II | 1.19  | 1.25                  | 1.31  | 0.18              | (1)                     | V <sub>CCIO</sub> /2 – 0.15  | V <sub>CCIO</sub> /2   | V <sub>CCIO</sub> /2 + 0.15  | 2(V <sub>IH(AC)</sub> - V <sub>REF</sub> ) | _                                             |

| SSTL-12<br>Class I, II  | 1.14  | 1.2                   | 1.26  | 0.18              | _                       | V <sub>REF</sub><br>-0.15    | V <sub>CCI0</sub> /2   | V <sub>REF</sub> + 0.15      | -0.30                                      | 0.30                                          |

## Note to Table 20:

Table 21. Differential HSTL and HSUL I/O Standards for Stratix V Devices (Part 1 of 2)

| I/O                    |       |     |       | V <sub>DIF(</sub> | <sub>DC)</sub> (V) |      | V <sub>X(AC)</sub> (V) |      |      | V <sub>CM(DC)</sub> (V | )    | V <sub>DIF(</sub> | <sub>(C)</sub> (V) |

|------------------------|-------|-----|-------|-------------------|--------------------|------|------------------------|------|------|------------------------|------|-------------------|--------------------|

| Standard               | Min   | Тур | Max   | Min               | Max                | Min  | Тур                    | Max  | Min  | Тур                    | Max  | Min               | Max                |