https://www.fpgamall.com

# THE DATASHEET OF FPGA

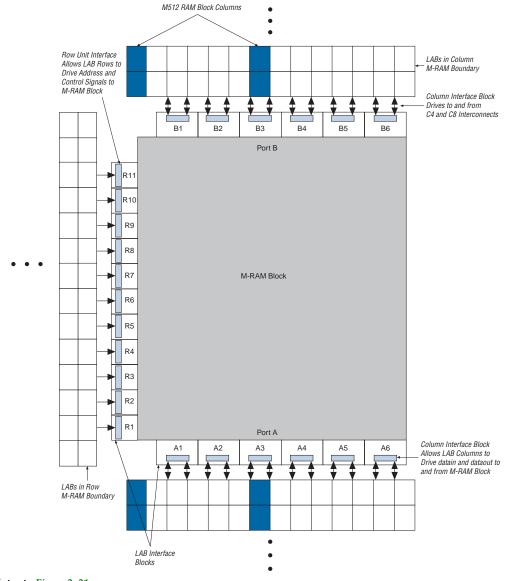

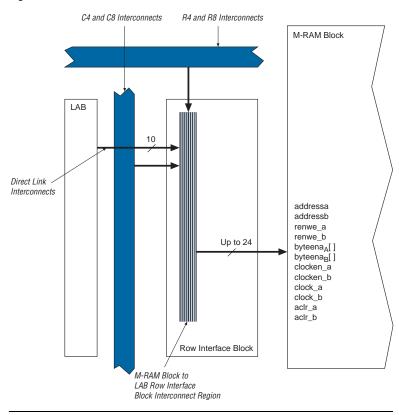

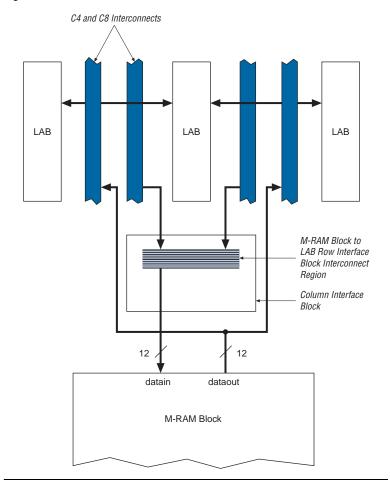

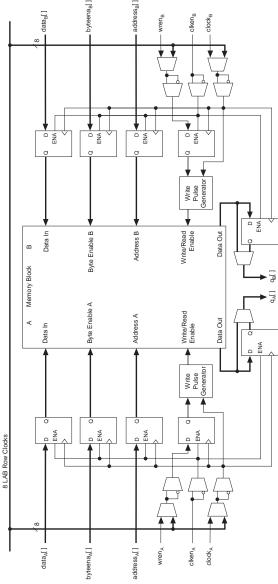

# Stratix Device Handbook, Volume 1

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com

#### EP1S25F672C6N Intel IC FPGA 473 I/O 672FBGA

Copyright © 2006 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and service at any time without notice. Altera assumes no repossibility or liability arging out of the an-

changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

I.S. EN ISO 9001

ii Altera Corporation

# **Contents**

| Chapter Revision Dates                      | vii      |

|---------------------------------------------|----------|

|                                             |          |

| About This Handbook                         |          |

| How to Find Information                     |          |

| How to Contact Altera                       |          |

| Typographic Conventions                     | x        |

| Section I. Stratix Device Family Data Sheet |          |

| Revision History                            | Part I–1 |

| Chapter 1. Introduction                     |          |

| Introduction                                | 1–1      |

| Features                                    | 1–2      |

| Chapter 2. Stratix Architecture             |          |

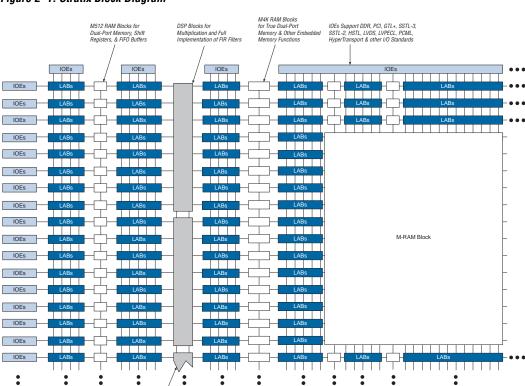

| Functional Description                      | 2–1      |

| Logic Array Blocks                          |          |

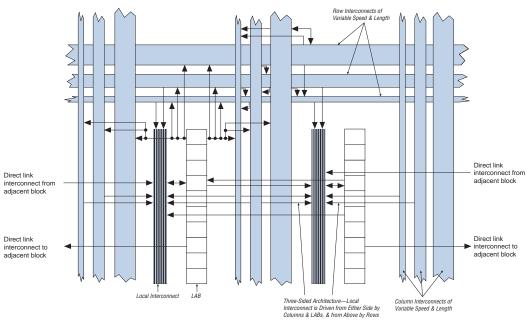

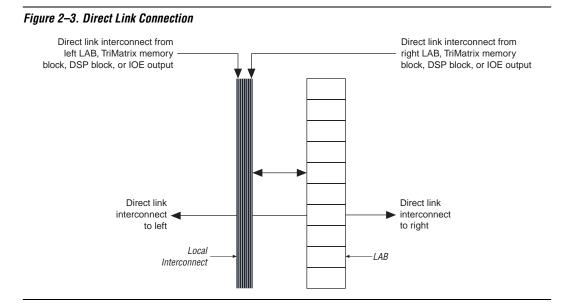

| LAB Interconnects                           |          |

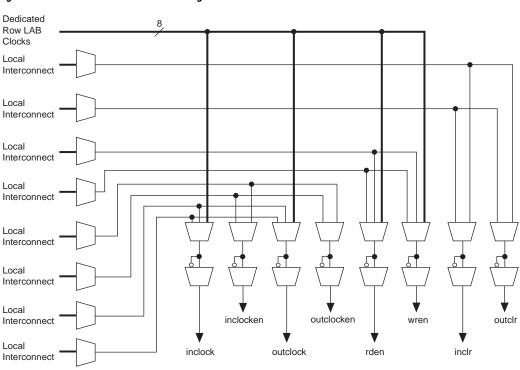

| LAB Control Signals                         |          |

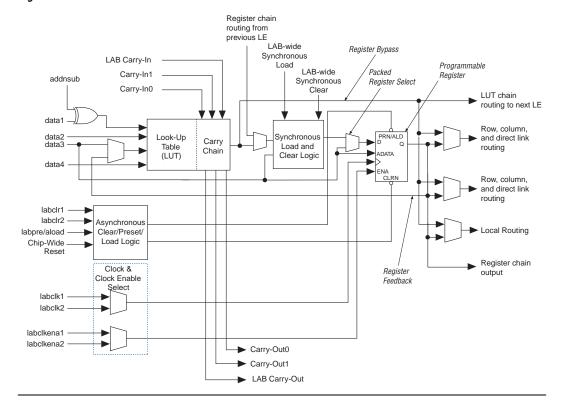

| Logic Elements                              |          |

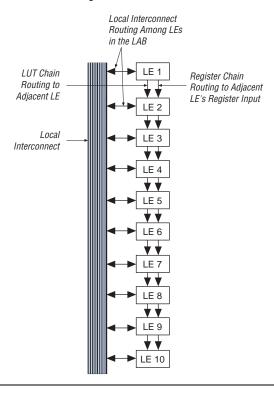

| LUT Chain & Register Chain                  |          |

| addnsub Signal                              |          |

| LE Operating Modes                          |          |

| Clear & Preset Logic Control                |          |

| MultiTrack Interconnect                     |          |

| TriMatrix Memory                            |          |

| Memory Modes                                |          |

| Clear Signals                               |          |

| Parity Bit Support                          |          |

| Shift Register Support                      |          |

| Memory Block Size                           |          |

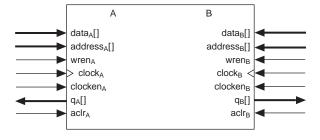

| Independent Clock Mode                      |          |

| Input/Output Clock Mode                     |          |

| Read/Write Clock Mode                       |          |

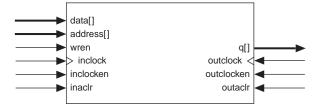

| Single-Port Mode                            |          |

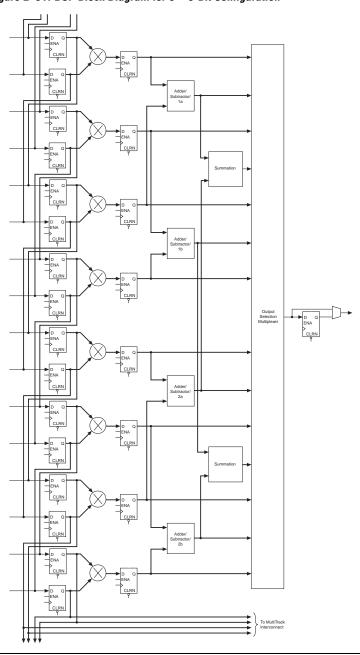

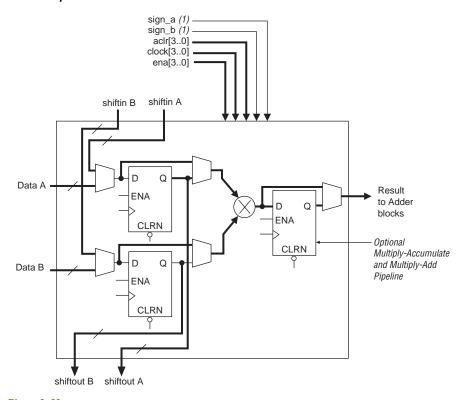

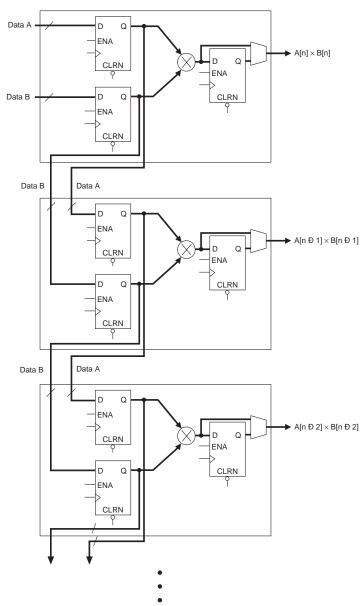

| Multiplier Block                            |          |

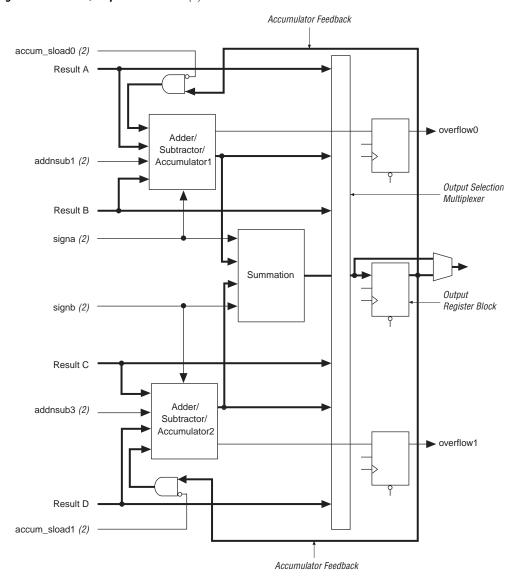

| Adder/Output Blocks                         |          |

| Modes of Operation                          |          |

| ±                                           |          |

| DSP Block Interface                                                                                                                                                                                                                                                                                                 | 2–70                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

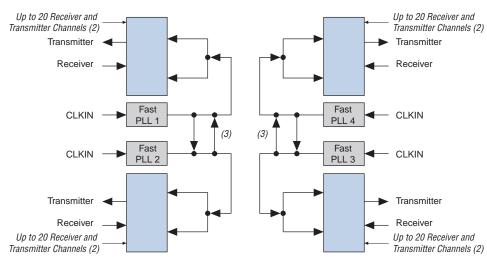

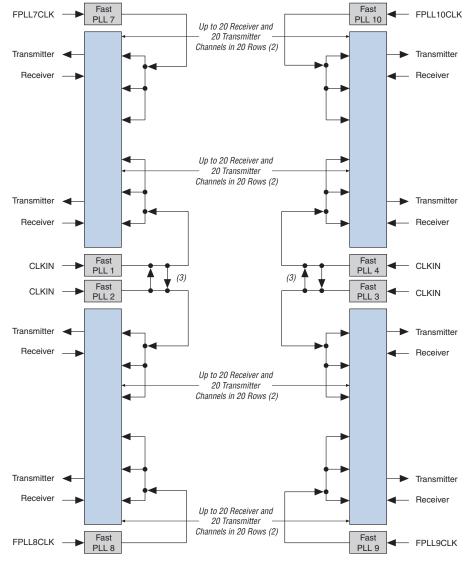

| PLLs & Clock Networks                                                                                                                                                                                                                                                                                               | 2–73                             |

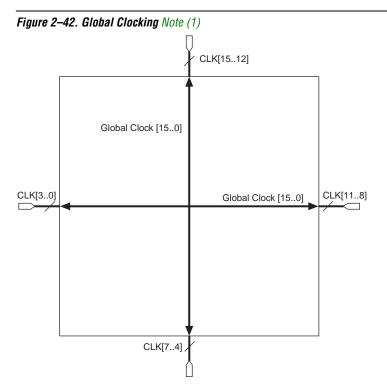

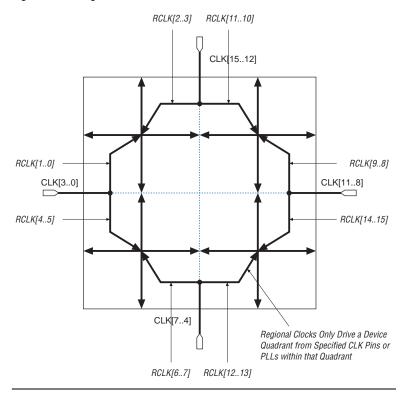

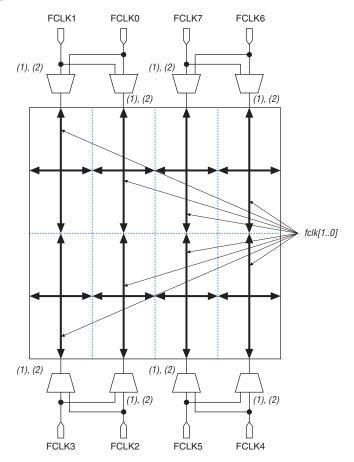

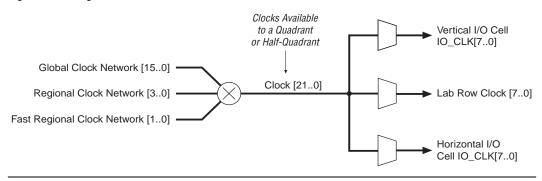

| Global & Hierarchical Clocking                                                                                                                                                                                                                                                                                      | 2–73                             |

| Enhanced & Fast PLLs                                                                                                                                                                                                                                                                                                |                                  |

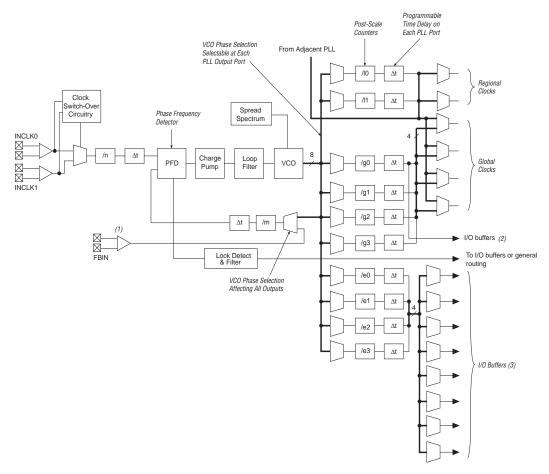

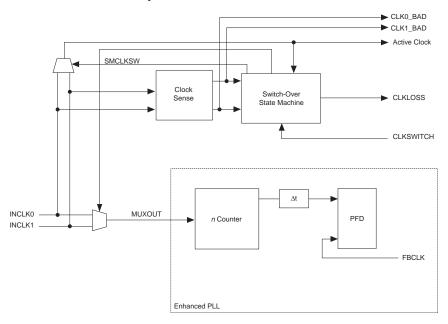

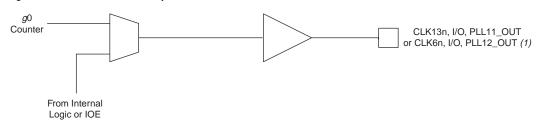

| Enhanced PLLs                                                                                                                                                                                                                                                                                                       | 2–87                             |

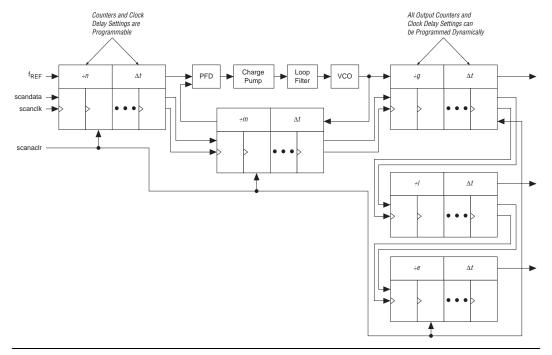

| Fast PLLs                                                                                                                                                                                                                                                                                                           | 2–100                            |

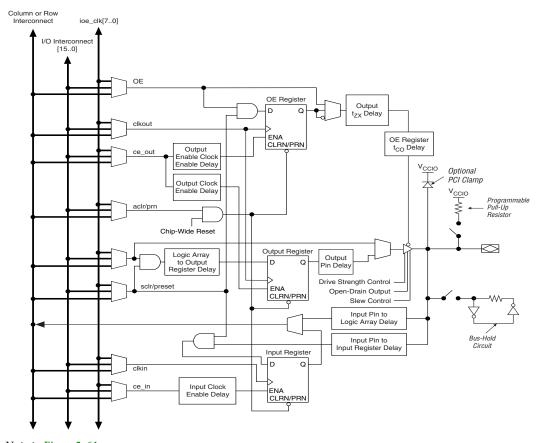

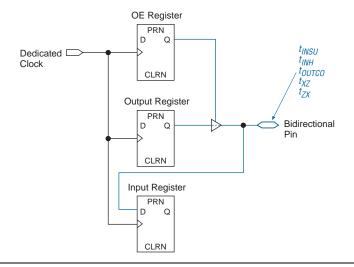

| I/O Structure                                                                                                                                                                                                                                                                                                       | 2–104                            |

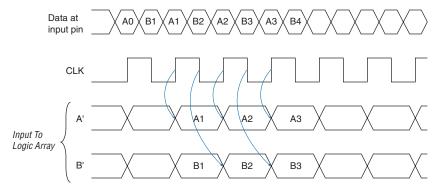

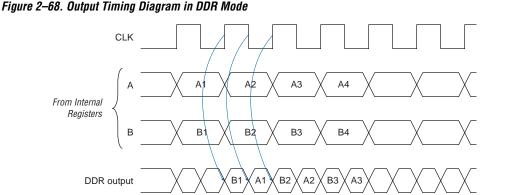

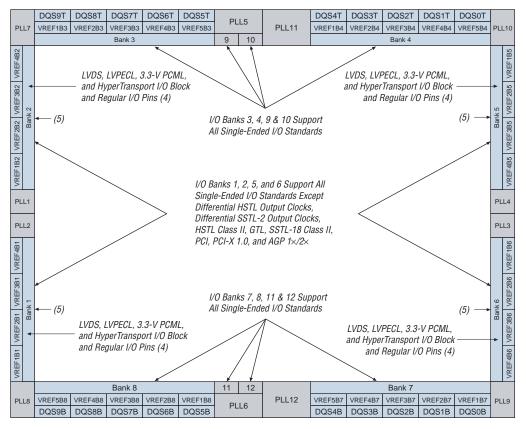

| Double-Data Rate I/O Pins                                                                                                                                                                                                                                                                                           | 2–111                            |

| External RAM Interfacing                                                                                                                                                                                                                                                                                            |                                  |

| Programmable Drive Strength                                                                                                                                                                                                                                                                                         | 2–119                            |

| Open-Drain Output                                                                                                                                                                                                                                                                                                   | 2–120                            |

| Slew-Rate Control                                                                                                                                                                                                                                                                                                   | 2–120                            |

| Bus Hold                                                                                                                                                                                                                                                                                                            |                                  |

| Programmable Pull-Up Resistor                                                                                                                                                                                                                                                                                       |                                  |

| Advanced I/O Standard Support                                                                                                                                                                                                                                                                                       |                                  |

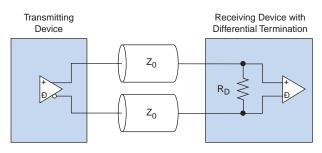

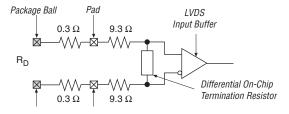

| Differential On-Chip Termination                                                                                                                                                                                                                                                                                    |                                  |

| MultiVolt I/O Interface                                                                                                                                                                                                                                                                                             |                                  |

| High-Speed Differential I/O Support                                                                                                                                                                                                                                                                                 |                                  |

| Dedicated Circuitry                                                                                                                                                                                                                                                                                                 |                                  |

| Byte Alignment                                                                                                                                                                                                                                                                                                      |                                  |

| Power Sequencing & Hot Socketing                                                                                                                                                                                                                                                                                    | 2–140                            |

| IEEE Std. 1149.1 (JTAG) Boundary-Scan Support SignalTap II Embedded Logic Analyzer Configuration Operating Modes Configuring Stratix FPGAs with JRunner Configuration Schemes Partial Reconfiguration Remote Update Configuration Modes Stratix Automated Single Event Upset (SEU) Detection Custom-Built Circuitry | 3–5 3–5 3–5 3–7 3–7 3–7 3–8 3–12 |

| Software Interface                                                                                                                                                                                                                                                                                                  | 3 12<br>2 12                     |

| Temperature Sensing Diode                                                                                                                                                                                                                                                                                           |                                  |

| Chapter 4. DC & Switching Characteristics Operating Conditions                                                                                                                                                                                                                                                      |                                  |

| Power Consumption                                                                                                                                                                                                                                                                                                   |                                  |

| Timing Model                                                                                                                                                                                                                                                                                                        |                                  |

| Preliminary & Final Timing                                                                                                                                                                                                                                                                                          |                                  |

| Performance                                                                                                                                                                                                                                                                                                         |                                  |

| Internal Timing Parameters                                                                                                                                                                                                                                                                                          |                                  |

| External Timing Parameters                                                                                                                                                                                                                                                                                          |                                  |

| Stratix External I/O Timing                                                                                                                                                                                                                                                                                         |                                  |

| I/O Timing Measurement Methodology                                                                                                                                                                                                                                                                                  |                                  |

| External I/O Delay Parameters                                                                                                                                                                                                                                                                                       | 4–66                             |

#### EP1S25F672C6N Intel IC FPGA 473 I/O 672FBGA

Contents

| Maximum Input & Output Clock Rates          | 4–76 |

|---------------------------------------------|------|

| High-Speed I/O Specification                |      |

| PLL Specifications                          |      |

| DLL Specifications                          |      |

| Chapter 5. Reference & Ordering Information |      |

| Software                                    | 5–1  |

| Device Pin-Outs                             | 5–1  |

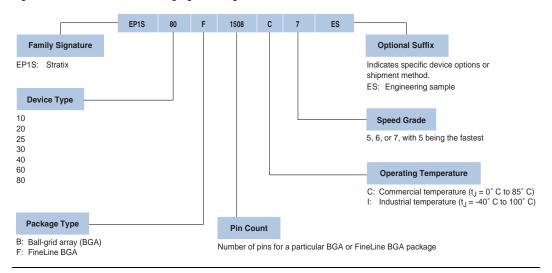

| Ordering Information                        | 5–1  |

|                                             |      |

#### Index

**Contents**

Altera Corporation v

Stratix Device Handbook, Volume 1

vi Altera Corporation

# **Chapter Revision Dates**

The chapters in this book, *Stratix Device Handbook*, *Volume 1*, were revised on the following dates. Where chapters or groups of chapters are available separately, part numbers are listed.

Chapter 1. Introduction

Revised: July 2005 Part number: S51001-3.2

Chapter 2. Stratix Architecture

Revised: July 2005 Part number: S51002-3.2

Chapter 3. Configuration & Testing

Revised: July 2005 Part number: S51003-1.3

Chapter 4. DC & Switching Characteristics

Revised: January 2006 Part number: S51004-3.4

Chapter 5. Reference & Ordering Information

Revised: September 2004 Part number: S51005-2.1

Altera Corporation vii

Stratix Device Handbook, Volume 1

viii Altera Corporation

## **About This Handbook**

This handbook provides comprehensive information about the Altera® Stratix family of devices.

# How to Find Information

You can find more information in the following ways:

- The Adobe Acrobat Find feature, which searches the text of a PDF document. Click the binoculars toolbar icon to open the Find dialog box.

- Acrobat bookmarks, which serve as an additional table of contents in PDF documents.

- Thumbnail icons, which provide miniature previews of each page, provide a link to the pages.

- Numerous links, shown in green text, which allow you to jump to related information.

### How to Contact Altera

For the most up-to-date information about Altera products, go to the Altera world-wide web site at www.altera.com. For technical support on this product, go to www.altera.com/mysupport. For additional information about Altera products, consult the sources shown below.

| Information Type               | USA & Canada                                                   | All Other Locations                                                    |

|--------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------|

| Technical support              | www.altera.com/mysupport/                                      | www.altera.com/mysupport/                                              |

|                                | (800) 800-EPLD (3753)<br>(7:00 a.m. to 5:00 p.m. Pacific Time) | +1 408-544-8767<br>7:00 a.m. to 5:00 p.m. (GMT -8:00)<br>Pacific Time  |

| Product literature             | www.altera.com                                                 | www.altera.com                                                         |

| Altera literature services     | literature@altera.com                                          | literature@altera.com                                                  |

| Non-technical customer service | (800) 767-3753                                                 | + 1 408-544-7000<br>7:00 a.m. to 5:00 p.m. (GMT -8:00)<br>Pacific Time |

| FTP site                       | ftp.altera.com                                                 | ftp.altera.com                                                         |

Altera Corporation ix

# Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                                                                                              |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: f <sub>MAX</sub> , \qdesigns directory, d: drive, chiptrip.gdf file.                                                                         |

| Italic Type with Initial Capital<br>Letters | Document titles are shown in italic type with initial capital letters. Example: AN 75: High-Speed Board Designs.                                                                                                                                                                                                        |

| Italic type                                 | Internal timing parameters and variables are shown in italic type. Examples: $t_{PlA}$ , $n+1$ .                                                                                                                                                                                                                        |

|                                             | Variable names are enclosed in angle brackets (< >) and shown in italic type. Example: <file name="">, <pre><pre><pre><pre><pre><pre>pof</pre> file.</pre></pre></pre></pre></pre></file>                                                                                                                               |

| Initial Capital Letters                     | Keyboard keys and menu names are shown with initial capital letters. Examples: Delete key, the Options menu.                                                                                                                                                                                                            |

| "Subheading Title"                          | References to sections within a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                                                            |

| Courier type                                | Signal and port names are shown in lowercase Courier type. Examples: $\mathtt{data1}$ , $\mathtt{tdi}$ , $\mathtt{input}$ . Active-low signals are denoted by suffix $\mathtt{n}$ , $\mathtt{e.g.}$ , $\mathtt{resetn}$ .                                                                                               |

|                                             | Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDESIGN), as well as logic function names (e.g., TRI) are shown in Courier. |

| 1., 2., 3., and<br>a., b., c., etc.         | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                        |

| • •                                         | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                    |

| ✓                                           | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                     |

|                                             | The hand points to information that requires special attention.                                                                                                                                                                                                                                                         |

| 4                                           | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                              |

| •••                                         | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                          |

x Altera Corporation

# Section I. Stratix Device Family Data Sheet

This section provides the data sheet specifications for Stratix<sup>®</sup> devices. They contain feature definitions of the internal architecture, configuration and JTAG boundary-scan testing information, DC operating conditions, AC timing parameters, a reference to power consumption, and ordering information for Stratix devices.

This section contains the following chapters:

- Chapter 1, Introduction

- Chapter 2, Stratix Architecture

- Chapter 3, Configuration & Testing

- Chapter 4, DC & Switching Characteristics

- Chapter 5, Reference & Ordering Information

#### **Revision History**

The table below shows the revision history for Chapters 1 through 5.

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                     |

|---------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | July 2005, v3.2      | Minor content changes.                                                                                                                                                                                                                                                                                                           |

|         | September 2004, v3.1 | • Updated Table 1–6 on page 1–5.                                                                                                                                                                                                                                                                                                 |

|         | April 2004, v3.0     | <ul> <li>Main section page numbers changed on first page.</li> <li>Changed PCI-X to PCI-X 1.0 in "Features" on page 1–2.</li> <li>Global change from SignalTap to SignalTap II.</li> <li>The DSP blocks in "Features" on page 1–2 provide dedicated implementation of multipliers that are now "faster than 300 MHz."</li> </ul> |

|         | January 2004, v2.2   | Updated -5 speed grade device information in Table 1-6.                                                                                                                                                                                                                                                                          |

|         | October 2003, v2.1   | Add -8 speed grade device information.                                                                                                                                                                                                                                                                                           |

|         | July 2003, v2.0      | Format changes throughout chapter.                                                                                                                                                                                                                                                                                               |

Altera Corporation Section I–1

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2       | July 2005 v3.2       | <ul> <li>Added "Clear Signals" section.</li> <li>Updated "Power Sequencing &amp; Hot Socketing" section.</li> <li>Format changes.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | September 2004, v3.1 | <ul> <li>Updated fast regional clock networks description on page 2–73.</li> <li>Deleted the word preliminary from the "specification for the maximum time to relock is 100 μs" on page 2–90.</li> <li>Added information about differential SSTL and HSTL outputs in "External Clock Outputs" on page 2–92.</li> <li>Updated notes in Figure 2–55 on page 2–93.</li> <li>Added information about <i>m</i> counter to "Clock Multiplication &amp; Division" on page 2–101.</li> <li>Updated Note 1 in Table 2–58 on page 2–101.</li> <li>Updated description of "Clock Multiplication &amp; Division" on page 2–88.</li> <li>Updated Table 2–22 on page 2–102.</li> <li>Added references to AN 349 and AN 329 to "External RAM Interfacing" on page 2–115.</li> <li>Table 2–25 on page 2–116: updated the table, updated Notes 3 and 4. Notes 4, 5, and 6, are now Notes 5, 6, and 7, respectively.</li> <li>Updated Table 2–26 on page 2–117.</li> <li>Added information about PCI Compliance to page 2–120.</li> <li>Table 2–32 on page 2–126: updated the table and deleted Note 1.</li> <li>Updated reference to device pin-outs now being available on the web on page 2–130.</li> <li>Added Notes 4 and 5 to Table 2–36 on page 2–130.</li> <li>Updated Note 5 in Table 2–41 on page 2–135.</li> </ul> |

|         | April 2004, v3.0     | <ul> <li>Added note 3 to rows 11 and 12 in Table 2–18.</li> <li>Deleted "Stratix and Stratix GX Device PLL Availability" table.</li> <li>Added I/O standards row in Table 2–28 that support max and min strength.</li> <li>Row clk [1,3,8,10] was removed from Table 2–30.</li> <li>Added checkmarks in Enhanced column for LVPECL, 3.3-V PCML, LVDS, and HyperTransport technology rows in Table 2–32.</li> <li>Removed the Left and Right I/O Banks row in Table 2–34.</li> <li>Changed RCLK values in Figures 2–50 and 2–51.</li> <li>External RAM Interfacing section replaced.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         | November 2003, v2.2  | <ul> <li>Added 672-pin BGA package information in Table 2–37.</li> <li>Removed support for series and parallel on-chip termination.</li> <li>Termination Technology renamed differential on-chip termination.</li> <li>Updated the number of channels per PLL in Tables 2-38 through 2-42.</li> <li>Updated Figures 2–65 and 2–67.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | October 2003, v2.1   | <ul> <li>Updated DDR I information.</li> <li>Updated Table 2–22.</li> <li>Added Tables 2–25, 2–29, 2–30, and 2–72.</li> <li>Updated Figures 2–59, 2–65, and 2–67.</li> <li>Updated the Lock Detect section.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Section I–2 Altera Corporation

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2       | July 2003, v2.0      | <ul> <li>Added reference on page 2-73 to Figures 2-50 and 2-51 for RCLK connections.</li> <li>Updated ranges for EPLL post-scale and pre-scale dividers on page 2-85.</li> <li>Updated PLL Reconfiguration frequency from 25 to 22 MHz on page 2-87.</li> <li>New requirement to assert are set signal each PLL when it has to reacquire lock on either a new clock after loss of lock (page 2-96).</li> <li>Updated max input frequency for CLK [1,3,8,10] from 462 to 500, Table 2-24.</li> <li>Renamed impedance matching to series termination throughout.</li> <li>Updated naming convention for DQS pins on page 2-112 to match pin tables.</li> <li>Added DDR SDRAM Performance Specification on page 2-117.</li> <li>Added external reference resistor values for terminator technology (page 2-136).</li> <li>Added Terminator Technology Specification on pages 2-137 and 2-138.</li> <li>Updated Tables 2-45 to 2-49 to reflect PLL cross-bank support for high speed differential channels at full speed.</li> <li>Wire bond package performance specification for "high" speed channels was increased to 624 Mbps from 462 Mbps throughout chapter.</li> </ul> |

| 3       | July 2005, v1.3      | <ul> <li>Updated "Operating Modes" section.</li> <li>Updated "Temperature Sensing Diode" section.</li> <li>Updated "IEEE Std. 1149.1 (JTAG) Boundary-Scan Support" section.</li> <li>Updated "Configuration" section.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | January 2005, v1.2   | Updated limits for JTAG chain of devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         | September 2004, v1.1 | <ul> <li>Added new section, "Stratix Automated Single Event Upset (SEU)         Detection" on page 3–12.</li> <li>Updated description of "Custom-Built Circuitry" on page 3–13.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | April 2003, v1.0     | No new changes in Stratix Device Handbook v2.0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4       | January 2006, v3.4   | Added Table 4–135.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | July 2005, v3.3      | <ul> <li>Updated Tables 4–6 and 4–30.</li> <li>Updated Tables 4–103 through 4–108.</li> <li>Updated Tables 4–114 through 4–124.</li> <li>Updated Table 4–129.</li> <li>Added Table 4–130.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Altera Corporation Section I–3

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       | January 2005, 3.2    | Updated rise and fall input values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

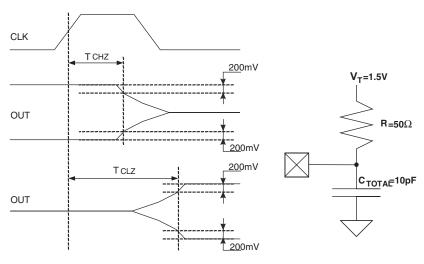

|         | September 2004, v3.1 | <ul> <li>Updated Note 3 in Table 4–8 on page 4–4.</li> <li>Updated Table 4–10 on page 4–6.</li> <li>Updated Table 4–20 on page 4–12 through Table 4–23 on page 4–13. Added rows V<sub>IL(AC)</sub> and V<sub>IH(AC)</sub> to each table.</li> <li>Updated Table 4–26 on page 4–14 through Table 4–29 on page 4–15.</li> <li>Updated Table 4–31 on page 4–16.</li> <li>Updated description of "External Timing Parameters" on page 4–33.</li> <li>Updated Table 4–36 on page 4–20.</li> <li>Added signals t<sub>OUTCO</sub>, T<sub>XZ</sub>, and T<sub>ZX</sub> to Figure 4–4 on page 4–33.</li> <li>Added rows t<sub>M512CLKENSU</sub> and t<sub>M512CLKENH</sub> to Table 4–40 on page 4–24.</li> <li>Added rows t<sub>M4CLKENSU</sub> and t<sub>M4CLKENH</sub> to Table 4–41 on page 4–24.</li> <li>Updated Note 2 in Table 4–54 on page 4–35.</li> <li>Added rows t<sub>MRAMCLKENSU</sub> and t<sub>MRAMCLKENH</sub> to Table 4–42 on page 4–25.</li> <li>Updated Table 4–46 on page 4–29.</li> <li>Updated Table 4–47 on page 4–29.</li> </ul> |

Section I–4 Altera Corporation

| Chapter   | Date/Version | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 4 | Date/Version | <ul> <li>Table 4–48 on page 4–30: added rows t<sub>M512CLKSENSU</sub> and t<sub>M512CLKENH</sub>, and updated symbol names.</li> <li>Updated power-up current (ICCINT) required to power a Stratix device on page 4–17.</li> <li>Updated Table 4–37 on page 4–22 through Table 4–43 on page 4–27.</li> <li>Table 4–49 on page 4–31: added rows t<sub>M4KCLKENSU</sub>, t<sub>M4KCLKENH</sub>, t<sub>M4KBESU</sub>, and t<sub>M4KBEH</sub>, deleted rows t<sub>M4KRADDRASU</sub> and t<sub>M4KRADDRH</sub>, and updated symbol names.</li> <li>Table 4–50 on page 4–31: added rows t<sub>MRAMADDRASU</sub> and t<sub>MRAMBESU</sub>, and t<sub>MRAMBEH</sub>, deleted rows t<sub>MRAMADDRASU</sub> and t<sub>MRAMBEH</sub>, and updated symbol names.</li> <li>Table 4–52 on page 4–34: updated table, deleted "Conditions" column, and added rows t<sub>XZ</sub> and t<sub>ZX</sub>.</li> <li>Table 4–52 on page 4–34: updated table, deleted "Conditions" column, and added rows t<sub>XZ</sub> and t<sub>ZX</sub>.</li> <li>Table 4–53 on page 4–34: updated table and added rows t<sub>XZPLL</sub> and t<sub>ZXPLL</sub>.</li> <li>Updated Note 2 in Table 4–53 on page 4–34.</li> <li>Table 4–54 on page 4–35: updated table, deleted "Conditions" column, and added rows t<sub>XZPLL</sub> and t<sub>ZXPLL</sub>.</li> <li>Updated Note 2 in Table 4–54 on page 4–35.</li> <li>Deleted Note 2 from Table 4–55 on page 4–36 through Table 4–66 on page 4–41.</li> <li>Updated Table 4–55 on page 4–36 through Table 4–96 on page 4–56. Added rows T<sub>XZ</sub>, T<sub>XZ</sub>, T<sub>XZPLL</sub>, and T<sub>ZXPLL</sub>.</li> <li>Added Note 1 to Table 4–67 on page 4–42 through Table 4–84 on page 4–50.</li> <li>Deleted Note 1 from Table 4–67 on page 4–42 through Table 4–84 on page 4–50.</li> <li>Deleted Note 1 from Table 4–85 on page 4–51 through Table 4–84 on page 4–56.</li> <li>Added Note 4 to Table 4–101 on page 4–62.</li> <li>Deleted Note 2 from Table 4–85 on page 4–51 through Table 4–84 on page 4–50.</li> <li>Deleted Note 2 from Table 4–85 on page 4–51 through Table 4–86 on page 4–50.</li> <li>Deleted Note 2 from Table 4–85 on page 4–51 through Table 4–86 on page 4–50.</li> <li>Deleted Note 1 from Table 4–85 on page 4–62.</li> <li>Table 4–102 on page 4–64: updated table and added Note 4.</li> <li>Updated de</li></ul> |

|           |              | page 4–66.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Altera Corporation Section I–5

| Chapter | Date/Version        | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       |                     | <ul> <li>Updated Table 4–123 on page 4–85 through Table 4–126 on page 4–92.</li> <li>Updated Note 3 in Table 4–123 on page 4–85.</li> <li>Table 4–125 on page 4–88: moved to correct order in chapter, and updated table.</li> <li>Updated Table 4–126 on page 4–92.</li> <li>Updated Table 4–127 on page 4–94.</li> <li>Updated Table 4–128 on page 4–95.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

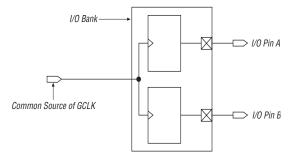

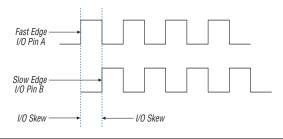

|         | April 2004, v3.0    | <ul> <li>Table 4–129 on page 4–96: updated table and added Note 10.</li> <li>Updated Table 4–131 and Table 4–132 on page 4–100.</li> <li>Updated Table 4–110 on page 4–74.</li> <li>Updated Table 4–123 on page 4–85.</li> <li>Updated Table 4–124 on page 4–87. through Table 4–126 on page 4–92.</li> <li>Added Note 10 to Table 4–129 on page 4–96.</li> <li>Moved Table 4–127 on page 4–94 to correct order in the chapter.</li> <li>Updated Table 4–131 on page 4–100 through Table 4–132 on page 4–100.</li> <li>Deleted t<sub>XZ</sub> and t<sub>ZX</sub> from Figure 4–4.</li> <li>Waveform was added to Figure 4–6.</li> <li>The minimum and maximum duty cycle values in Note 3 of Table 4–8 were moved to a new Table 4–9.</li> <li>Changes were made to values in SSTL-3 Class I and II rows in Table 4–17.</li> <li>Note 1 was added to Table 4–34.</li> <li>Added t<sub>SU_R</sub> and t<sub>SU_C</sub> rows in Table 4–38.</li> <li>Changed Table 4–55 title from "EP1S10 Column Pin Fast Regional Clock External I/O Timing Parameters" to "EP1S10 External I/O Timing on Column Pins Using Fast Regional Clock Networks."</li> <li>Changed values in Tables 4–46, 4–48 to 4–51, 4–128, and 4–131.</li> <li>Added t<sub>ARESET</sub> row in Tables 4–127 to 4–132.</li> <li>Deleted -5 Speed Grade column in Tables 4–117 to 4–119 and 4–122 to 4–123.</li> <li>Fixed differential waveform in Figure 4–1.</li> <li>Added "Definition of I/O Skew" section.</li> <li>Added d'Definition of I/O Skew" section.</li> <li>Added table 4–46.</li> <li>Values changed in the t<sub>MAKCLKHL</sub> row in Table 4–47.</li> <li>Values changed in the t<sub>MAKCLKHL</sub> row in Table 4–50.</li> <li>Added Table 4–51 to "Internal Timing Parameters" section.</li> <li>The timing information is preliminary in Tables 4–55 through 4–96.</li> <li>Table 4–111 was separated into 3 tables: Tables 4–111 to 4–113.</li> </ul> |

|         | November 2003, v2.2 | Updated Tables 4–127 through 4–129.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

Section I–6 Altera Corporation

| Chapter | Date/Version         | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       | October 2003, v2.1   | <ul> <li>Added -8 speed grade information.</li> <li>Updated performance information in Table 4–36.</li> <li>Updated timing information in Tables 4–55 through 4–96.</li> <li>Updated delay information in Tables 4–103 through 4–108.</li> <li>Updated programmable delay information in Tables 4–100 and 4–103.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | July 2003, v2.0      | <ul> <li>Updated clock rates in Tables 4–114 through 4–123.</li> <li>Updated speed grade information in the introduction on page 4-1.</li> <li>Corrected figures 4-1 &amp; 4-2 and Table 4-9 to reflect how VID and VOD are specified.</li> <li>Added note 6 to Table 4-32.</li> <li>Updated Stratix Performance Table 4-35.</li> <li>Updated EP1S60 and EP1S80 timing parameters in Tables 4-82 to 4-93. The Stratix timing models are final for all devices.</li> <li>Updated Stratix IOE programmable delay chains in Tables 4-100 to 4-101.</li> <li>Added single-ended I/O standard output pin delay adders for loading in Table 4-102.</li> <li>Added spec for FPLL[107]CLK pins in Tables 4-104 and 4-107.</li> <li>Updated high-speed I/O specification for J=2 in Tables 4-114 and 4-115.</li> <li>Updated EPLL specification and fast PLL specification in Tables 4-116 to 4-120.</li> </ul> |

| 5       | September 2004, v2.1 | <ul> <li>Updated reference to device pin-outs on page 5–1 to indicate that<br/>device pin-outs are no longer included in this manual and are now<br/>available on the Altera web site.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|         | April 2003, v1.0     | No new changes in Stratix Device Handbook v2.0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Altera Corporation Section I–7

Stratix Device Handbook, Volume 1

Section I–8 Altera Corporation

### 1. Introduction

\$51001-3.2

#### Introduction

The Stratix® family of FPGAs is based on a 1.5-V, 0.13- $\mu$ m, all-layer copper SRAM process, with densities of up to 79,040 logic elements (LEs) and up to 7.5 Mbits of RAM. Stratix devices offer up to 22 digital signal processing (DSP) blocks with up to 176 (9-bit × 9-bit) embedded multipliers, optimized for DSP applications that enable efficient implementation of high-performance filters and multipliers. Stratix devices support various I/O standards and also offer a complete clock management solution with its hierarchical clock structure with up to 420-MHz performance and up to 12 phase-locked loops (PLLs).

The following shows the main sections in the Stratix Device Family Data Sheet:

| Section                                       | Page  |

|-----------------------------------------------|-------|

| Features                                      | 1–2   |

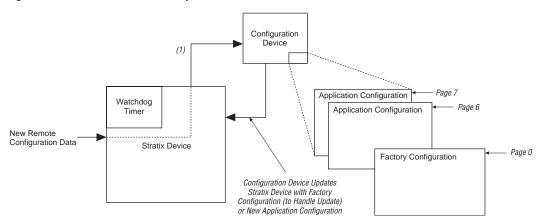

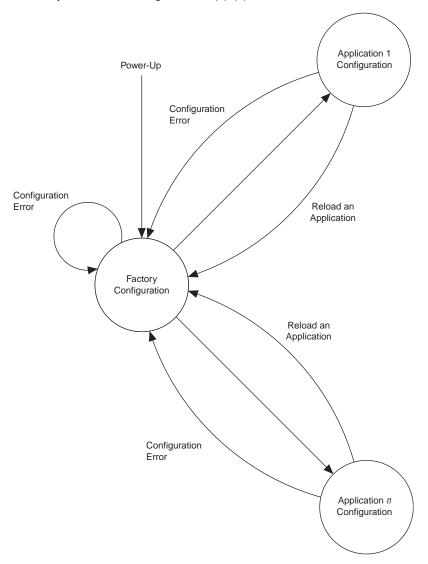

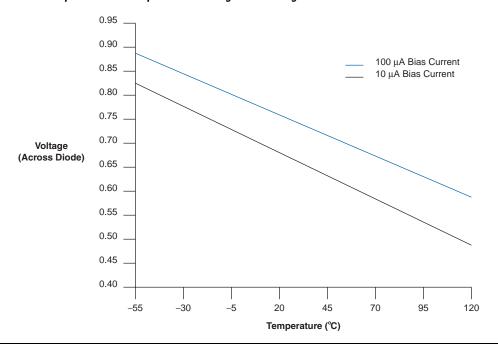

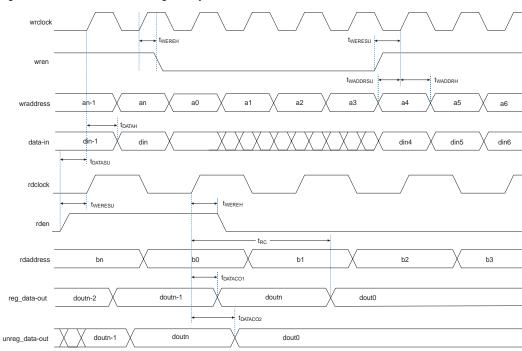

| Functional Description                        | 2–1   |