https://www.fpgamall.com

# THE DATASHEET OF FPGA

# XA Spartan-3A DSP Automotive FPGA Family Data Sheet

DS705 (v2.0) April 18, 2011

**Product Specification**

# **Summary**

The Xilinx Automotive (XA) Spartan®-3A DSP family of FPGAs solves the design challenges in most high-volume, cost-sensitive, high-performance DSP automotive applications. The two-member family offers densities ranging from 1.8 to 3.4 million system gates, as shown in Table 1.

# Introduction

XA devices are available in both extended-temperature Q-Grade ( $-40^{\circ}$ C to  $+125^{\circ}$ C T<sub>J</sub>) and I-Grade ( $-40^{\circ}$ C to  $+100^{\circ}$ C T<sub>J</sub>) and are qualified to the industry recognized AEC-Q100 standard.

The XA Spartan-3A DSP family builds on the success of the earlier XA Spartan-3E and XA Spartan-3 FPGA families by adding hardened DSP MACs with pre-adders, significantly increasing the throughput and performance of this low-cost family. These XA Spartan-3A DSP family enhancements, combined with proven 90 nm process technology, deliver more functionality and bandwidth per dollar than ever before, setting the new standard in the programmable logic industry.

Because of their exceptionally low cost,

XA Spartan-3A DSP FPGAs are ideally suited to a wide range of automotive electronics applications, including infotainment, driver information, and driver assistance modules.

The XA Spartan-3A DSP family is a superior alternative to mask programmed ASICs. FPGAs avoid the high initial mask set costs and lengthy development cycles, while also permitting design upgrades in the field with no hardware replacement necessary because of its inherent programmability, an impossibility with conventional ASICs and ASSPs with their inflexible architecture.

#### **Features**

- Very low cost, high-performance DSP solution for high-volume, cost-conscious applications

- 250 MHz DSP48A slices using XtremeDSP™ solution

- Dedicated 18-bit by 18-bit multiplier

- Available pipeline stages for enhanced performance of at least 250 MHz in the standard -4 speed grade

- 48-bit accumulator for multiply-accumulate (MAC) operation

- Integrated adder for complex multiply or multiply-add operation

- Integrated 18-bit pre-adder

- Optional cascaded Multiply or MAC

- Dual-range V<sub>CCAUX</sub> supply simplifies 3.3V-only design

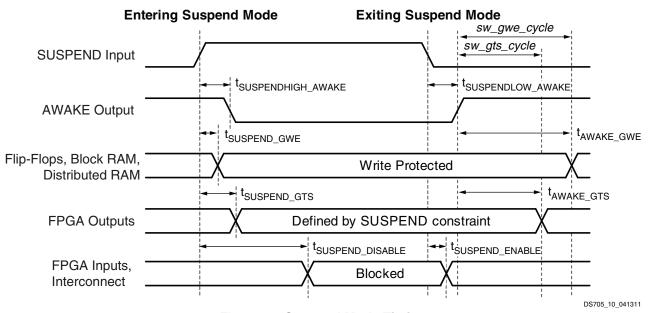

- Suspend and Hibernate modes reduce system power

- Multi-voltage, multi-standard SelectIO™ interface pins

- Up to 519 I/O pins or 227 differential signal pairs

- LVCMOS, LVTTL, HSTL, and SSTL single-ended I/O

- 3.3V, 2.5V, 1.8V, 1.5V, and 1.2V signaling

- Selectable output drive, up to 24 mA per pin

- QUIETIO standard reduces I/O switching noise

- Full 3.3V ± 10% compatibility and hot-swap compliance

- 622+ Mb/s data transfer rate per differential I/O

- LVDS, RSDS, mini-LVDS, HSTL/SSTL differential I/O with integrated differential termination resistors

- Enhanced Double Data Rate (DDR) support

- DDR/DDR2 SDRAM support up to 266 Mb/s

- Fully compliant 32-bit, 33 MHz PCI® technology support

- Abundant, flexible logic resources

- Densities up to 53,712 logic cells, including optional shift register

- Efficient wide multiplexers, wide logic

- Fast look-ahead carry logic

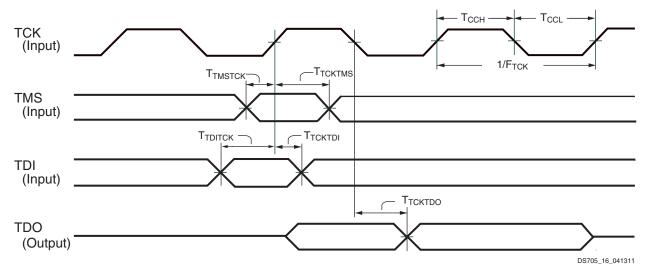

- IEEE 1149.1/1532 JTAG programming/debug port

- Hierarchical SelectRAM™ memory architecture

- Up to 2,268 Kbits of fast block RAM with byte write enables for processor applications

- Up to 373 Kbits of efficient distributed RAM

- Registered outputs on the block RAM with operation of at least 280 MHz in the standard -4 speed grade

- Eight Digital Clock Managers (DCMs)

- Clock skew elimination (delay locked loop)

- Frequency synthesis, multiplication, division

- · High-resolution phase shifting

- Wide frequency range (5 MHz to over 320 MHz)

- Eight low-skew global clock networks, eight additional clocks per half device, plus abundant low-skew routing

- Configuration interface to industry-standard PROMs

- Low-cost, space-saving SPI serial Flash PROM

- x8 or x8/x16 parallel NOR Flash PROM

- Unique Device DNA identifier for design authentication

- Complete Xilinx <u>ISE</u>® and <u>WebPACK</u>™ software support plus <u>Spartan-3A DSP FPGA Starter Kit</u>

- MicroBlaze<sup>™</sup> and PicoBlaze<sup>™</sup> embedded processor cores

- BGA packaging, Pb-free only

- Common footprints support easy density migration

© Copyright 2008–2011 Xilinx, Inc., Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI, PCI Express, PCIe, and PCI-X are trademarks of PCI-SIG. All other trademarks are the property of their respective owners.

Table 1: Summary of XA Spartan-3A DSP FPGA Attributes

| Device     | System | Equivalent<br>Logic | (On  | CLB A<br>e CLB = F |               | ces)            | Distributed             | Block<br>RAM | Dedicated<br>Multipliers | DCMe   | Maximum  | Maximum<br>Differential |

|------------|--------|---------------------|------|--------------------|---------------|-----------------|-------------------------|--------------|--------------------------|--------|----------|-------------------------|

| Device     | Ğates  | 0-11-               | Rows | Columns            | Total<br>CLBs | Total<br>Slices | RAM bits <sup>(1)</sup> | Bits<br>(1)  | Multipliers              | DCIVIS | User I/O | I/O Pairs               |

| XA3SD1800A | 1800K  | 37,440              | 88   | 48                 | 4,160         | 16,640          | 260K                    | 1512K        | 84                       | 8      | 519      | 227                     |

| XA3SD3400A | 3400K  | 53,712              | 104  | 58                 | 5,968         | 23,872          | 373K                    | 2268K        | 126                      | 8      | 469      | 213                     |

1. By convention, one Kb is equivalent to 1,024 bits.

Refer to <u>DS610</u>, *Spartan-3A DSP FPGA Family Data Sheet* for a full product description, AC and DC specifications, and package pinout descriptions. Any values shown specifically in this XA Spartan-3A DSP Automotive FPGA Family data sheet override those shown in DS610.

For information regarding reliability qualification, refer to RPT103, *Xilinx Spartan-3A Family Automotive Qualification Report* and RPT070, *Spartan-3A Commercial Qualification Report*. Contact your local Xilinx representative for more details on these reports.

# **Key Feature Differences from Commercial XC Devices**

- AEC-Q100 device qualification and full production part approval process (PPAP) documentation support available in both extended temperature I- and Q-Grades

- Guaranteed to meet full electrical specifications over the  $T_{I} = -40^{\circ}$ C to +125°C temperature range (Q-Grade)

- XA Spartan-3A DSP devices are available in the -4 speed grade only

- PCI-66 and PCI-X are not supported in the XA Spartan-3A DSP FPGA product line

- Platform Flash is not supported within the XA family

- XA Spartan-3A DSP devices are available in Pb-free packaging only

- MultiBoot is not supported in XA versions of this product.

- The XA Spartan-3A DSP device must be power cycled prior to reconfiguration.

# **Architectural Overview**

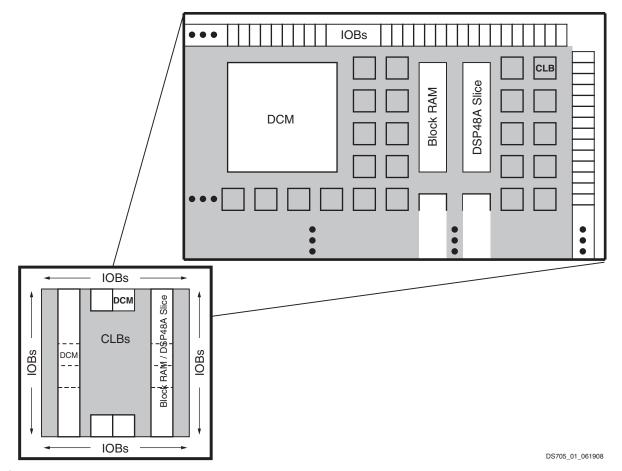

The XA Spartan-3A DSP family architecture consists of five fundamental programmable functional elements:

- **XtremeDSP DSP48A Slice** provides an 18-bit x 18-bit multiplier, 18-bit pre-adder, 48-bit post-adder/accumulator, and cascade capabilities for various DSP applications.

- Configurable Logic Blocks (CLBs) contain flexible Look-Up Tables (LUTs) that implement logic plus storage elements used as flip-flops or latches. CLBs perform a wide variety of logical functions as well as store data.

- Input/Output Blocks (IOBs) control the flow of data between the I/O pins and the internal logic of the device. IOBs support bidirectional data flow plus 3-state operation. Supports a variety of signal standards, including several high-performance differential standards. Double Data-Rate (DDR) registers are included.

- Block RAM provides data storage in the form of 18-Kb dual-port blocks.

- **Digital Clock Manager (DCM) Blocks** provide self-calibrating, fully digital solutions for distributing, delaying, multiplying, dividing, and phase-shifting clock signals.

These elements are organized as shown in Figure 1. A dual ring of staggered IOBs surrounds a regular array of CLBs. The XA3SD1800A has four columns of DSP48A slices, and the XA3SD3400A has five columns of DSP48A slices. Each DSP48A has an associated block RAM. The DCMs are positioned in the center with two at the top and two at the bottom of the device and in the two outer columns of the four or five columns of block RAM and DSP48As.

The XA Spartan-3A DSP family features a rich network of routing that interconnect all five functional elements, transmitting signals among them. Each functional element has an associated switch matrix that permits multiple connections to the routing.

- 1. The XA3SD1800A and XA3SD3400A have two DCMs on both the left and right sides, as well as the two DCMs at the top and bottom of the devices. The two DCMs on the left and right of the chips are in the middle of the outer block RAM/DSP48A columns of the four or five columns in the selected device, as shown in the diagram.

- 2. A detailed diagram of the DSP48A can be found in UG431, XtremeDSP DSP48A for Spartan-3A DSP FPGAs User Guide.

Figure 1: XA Spartan-3A DSP Family Architecture

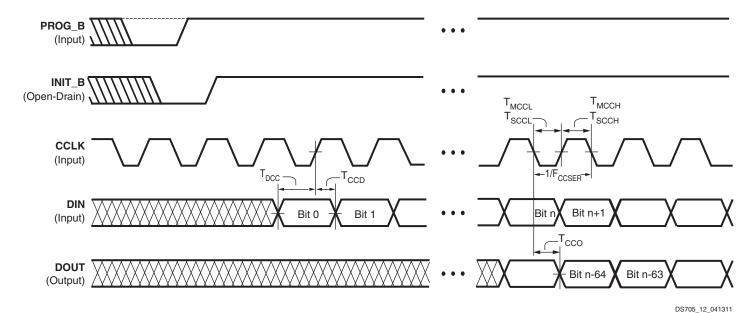

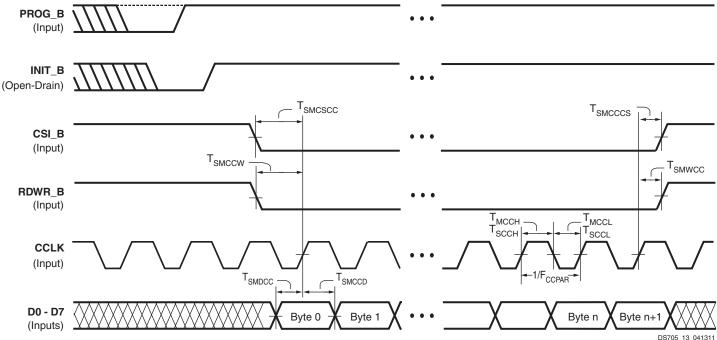

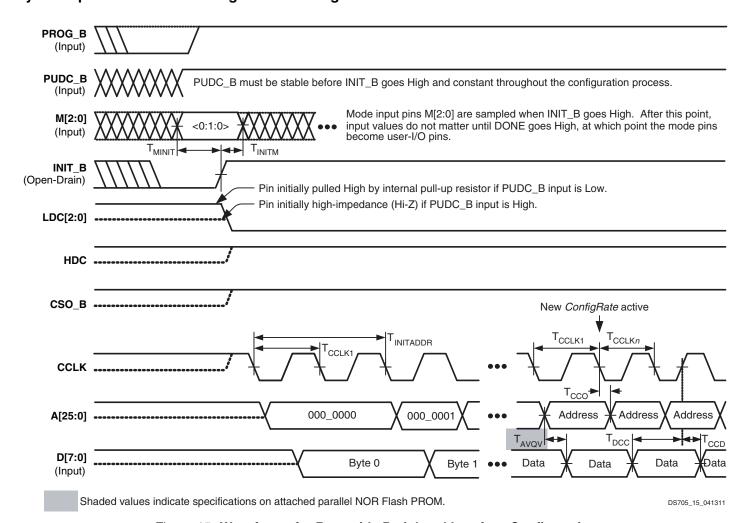

# Configuration

XA Spartan-3A DSP FPGAs are programmed by loading configuration data into robust, reprogrammable, static CMOS configuration latches (CCLs) that collectively control all functional elements and routing resources. The FPGA's configuration data is stored externally in a PROM or some other non-volatile medium, either on or off the board.

After applying power, the configuration data is written to the FPGA using any of five different modes:

- Serial Peripheral Interface (SPI) from an industry-standard SPI serial Flash

- Byte Peripheral Interface (BPI) Up from an industry-standard x8 or x8/x16 parallel NOR Flash

- Slave Serial, typically downloaded from a processor

- Slave Parallel, typically downloaded from a processor

- Boundary-scan (JTAG), typically downloaded from a processor or system tester

Additionally, each XA Spartan-3A DSP FPGA contains a unique, factory-programmed Device DNA identifier useful for tracking purposes, anti-cloning designs, or IP protection.

# I/O Capabilities

The XA Spartan-3A DSP FPGA SelectIO interface supports many popular single-ended and differential standards. Table 2 shows the number of user I/Os as well as the number of differential I/O pairs available for each device/package combination. Some of the user I/Os are unidirectional input-only pins as indicated in Table 2.

XA Spartan-3A DSP FPGAs support the following single-ended standards:

- 3.3V low-voltage TTL (LVTTL)

- Low-voltage CMOS (LVCMOS) at 3.3V, 2.5V, 1.8V, 1.5V, or 1.2V

- 3.3V PCI at 33 MHz

- HSTL I, II, and III at 1.5V and 1.8V, commonly used in memory applications

- SSTL I and II at 1.8V, 2.5V, and 3.3V, commonly used for memory applications

XA Spartan-3A DSP FPGAs support the following differential standards:

- LVDS, mini-LVDS, RSDS, and PPDS I/O at 2.5V or 3.3V

- Bus LVDS I/O at 2.5V

- TMDS I/O at 3.3V

- Differential HSTL and SSTL I/O

- LVPECL inputs at 2.5V or 3.3V

Table 2: Available User I/Os and Differential I/O Pairs

| Device     | CS              | G484         | FGG676              |                     |  |

|------------|-----------------|--------------|---------------------|---------------------|--|

| Device     | User            | Differential | User                | Differential        |  |

| XA3SD1800A | <b>309</b> (60) | 140<br>(78)  | <b>519</b><br>(110) | <b>227</b><br>(131) |  |

| XA3SD3400A | <b>309</b> (60) | 140<br>(78)  | <b>469</b> (60)     | <b>213</b> (117)    |  |

#### Notes:

# **Production Status**

Table 3 indicates the production status of each XA Spartan-3A DSP FPGA by temperature range and speed grade. The table also lists the earliest speed file version required for creating a production configuration bitstream. Later versions are also supported.

Table 3: XA Spartan-3A DSP FPGA Family Production Status (Production Speed File)

| Temperat    | ure Range  | I-Grade            | Q-Grade            |

|-------------|------------|--------------------|--------------------|

| Speed       | Grade      | Standard (-4)      | Standard (-4)      |

| Part Number | XA3SD1800A | Production (v1.32) | Production (v1.32) |

| Fait Number | XA3SD3400A | Production (v1.32) | -                  |

<sup>1.</sup> The number shown in **bold** indicates the maximum number of I/O and input-only pins. The number shown in (*italics*) indicates the number of input-only pins. The differential input-only pin count includes both differential pairs on input-only pins and differential pairs on I/O pins within I/O banks that are restricted to differential inputs.

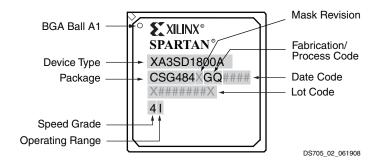

# **Package Marking**

Figure 2 shows the top marking for XA Spartan-3A DSP FPGAs in BGA packages.

Figure 2: XA Spartan-3A DSP FPGA Package Marking Example

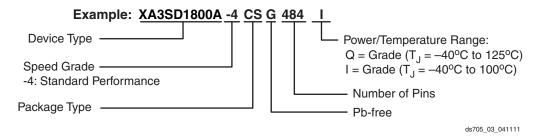

# **Ordering Information**

XA Spartan-3A DSP FPGAs are available in Pb-free packaging only for all device/package combinations.

# **Pb-Free Packaging**

Figure 3: Ordering Information

| Device     |    | Speed Grade             |        | Package Type / Number of Pins               | Temperature Range |                          |

|------------|----|-------------------------|--------|---------------------------------------------|-------------------|--------------------------|

| XA3SD1800A | -4 | Standard<br>Performance | CSG484 | 484-ball Chip-Scale Ball Grid Array (CSBGA) | I                 | I-Grade (-40°C to 100°C) |

| XA3SD3400A |    | •                       | FGG676 | 676-ball Fine-Pitch Ball Grid Array (FBGA)  | Q                 | Q-Grade (-40°C to 125°C) |

- 1. The XA Spartan-3A DSP FPGA product line is available in -4 speed grade only.

- 2. The XA3SD3400A is available in I-Grade only.

# **DC Electrical Characteristics**

All parameter limits are representative of worst-case supply voltage and junction temperature conditions. Unless otherwise noted, the published parameter values apply to all XA Spartan-3A DSP devices. AC and DC characteristics are specified using the same numbers for both I-Grade and Q-Grade.

# **Absolute Maximum Ratings**

Stresses beyond those listed under Table 4, *Absolute Maximum Ratings* might cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions beyond those listed under the Recommended Operating Conditions is not implied. Exposure to absolute maximum conditions for extended periods of time adversely affects device reliability.

Table 4: Absolute Maximum Ratings

| Symbol             | Description                                                | Conditions                              | Min   | Max                   | Units |

|--------------------|------------------------------------------------------------|-----------------------------------------|-------|-----------------------|-------|

| V <sub>CCINT</sub> | Internal supply voltage                                    |                                         | -0.5  | 1.32                  | V     |

| V <sub>CCAUX</sub> | Auxiliary supply voltage                                   |                                         | -0.5  | 3.75                  | V     |

| V <sub>CCO</sub>   | Output driver supply voltage                               |                                         | -0.5  | 3.75                  | V     |

| V <sub>REF</sub>   | Input reference voltage                                    |                                         | -0.5  | V <sub>CCO</sub> +0.5 | V     |

| V <sub>IN</sub>    | Voltage applied to all User I/O pins and Dual-Purpose pins | Driver in a high-impedance state        | -0.95 | 4.6                   | V     |

|                    | Voltage applied to all Dedicated pins                      | -0.5                                    | 4.6   | V                     |       |

| I <sub>IK</sub>    | Input clamp current per I/O pin                            | $-0.5V < V_{IN} < (V_{CCO} + 0.5V)$ (1) | _     | ±100                  | mA    |

|                    |                                                            | Human body model                        | _     | ±2000                 | V     |

| $V_{ESD}$          | Electrostatic Discharge Voltage                            | Charged device model                    | -     | ±500                  | V     |

|                    |                                                            | Machine model                           | _     | ±200                  | V     |

| $T_J$              | Junction temperature                                       | ,                                       | _     | 125                   | °C    |

| T <sub>STG</sub>   | Storage temperature                                        |                                         | -65   | 150                   | °C    |

- 1. Upper clamp applies only when using PCI IOSTANDARDs.

- 2. For soldering guidelines, see <u>UG112</u>: Device Packaging and Thermal Characteristics and <u>XAPP427</u>: Implementation and Solder Reflow Guidelines for Pb-Free Packages.

# **Power Supply Specifications**

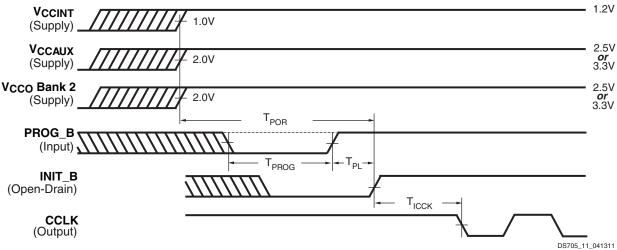

#### Table 5: Supply Voltage Thresholds for Power-On Reset

| Symbol              | Description                                      | Min | Max | Units |

|---------------------|--------------------------------------------------|-----|-----|-------|

| V <sub>CCINTT</sub> | Threshold for the V <sub>CCINT</sub> supply      | 0.4 | 1.0 | V     |

| V <sub>CCAUXT</sub> | Threshold for the V <sub>CCAUX</sub> supply      | 0.8 | 2.0 | V     |

| V <sub>CCO2T</sub>  | Threshold for the V <sub>CCO</sub> Bank 2 supply | 0.8 | 2.0 | V     |

#### Notes:

- V<sub>CCINT</sub>, V<sub>CCAUX</sub>, and V<sub>CCO</sub> supplies to the FPGA can be applied in any order. However, the FPGA's configuration source (SPI Flash, parallel NOR Flash, microcontroller) might have specific requirements. Check the data sheet for the attached configuration source. Apply V<sub>CCINT</sub> last for lowest overall power consumption (see <u>UG331</u> chapter "Powering Spartan-3 Generation FPGAs" for more information).

- To ensure successful power-on, V<sub>CCINT</sub>, V<sub>CCO</sub> Bank 2, and V<sub>CCAUX</sub> supplies must rise through their respective threshold-voltage ranges with no dips at any point.

#### Table 6: Supply Voltage Ramp Rate

| Symbol              | Description                                                      | Min | Max | Units |

|---------------------|------------------------------------------------------------------|-----|-----|-------|

| V <sub>CCINTR</sub> | Ramp rate from GND to valid V <sub>CCINT</sub> supply level      | 0.2 | 100 | ms    |

| V <sub>CCAUXR</sub> | Ramp rate from GND to valid V <sub>CCAUX</sub> supply level      | 0.2 | 100 | ms    |

| V <sub>CCO2R</sub>  | Ramp rate from GND to valid V <sub>CCO</sub> Bank 2 supply level | 0.2 | 100 | ms    |

#### Notes:

- V<sub>CCINT</sub>, V<sub>CCAUX</sub>, and V<sub>CCO</sub> supplies to the FPGA can be applied in any order. However, the FPGA's configuration source (SPI Flash, parallel NOR Flash, microcontroller) might have specific requirements. Check the data sheet for the attached configuration source. Apply V<sub>CCINT</sub> last for lowest overall power consumption (see <u>UG331</u> chapter "Powering Spartan-3 Generation FPGAs" for more information).

- To ensure successful power-on, V<sub>CCINT</sub>, V<sub>CCO</sub> Bank 2, and V<sub>CCAUX</sub> supplies must rise through their respective threshold-voltage ranges with no dips at any point.

## Table 7: Supply Voltage Levels Necessary for Preserving CMOS Configuration Latch (CCL) Contents and RAM Data

| Symbol             | Description                                                                             | Min | Units |

|--------------------|-----------------------------------------------------------------------------------------|-----|-------|

| V <sub>DRINT</sub> | V <sub>CCINT</sub> level required to retain CMOS Configuration Latch (CCL) and RAM data | 1.0 | V     |

| $V_{DRAUX}$        | V <sub>CCAUX</sub> level required to retain CMOS Configuration Latch (CCL) and RAM data | 2.0 | V     |

# **General Recommended Operating Conditions**

# Table 8: General Recommended Operating Conditions

| Symbol                          | D                                       | Description              |                          |      | Nominal | Max                   | Units |

|---------------------------------|-----------------------------------------|--------------------------|--------------------------|------|---------|-----------------------|-------|

| TJ                              | Junction temperature                    | I-Grade                  |                          | -40  | -       | 100                   | °C    |

|                                 |                                         | Q-Grade                  |                          | -40  | -       | 125                   | °C    |

| V <sub>CCINT</sub>              | Internal supply voltage                 |                          |                          | 1.14 | 1.20    | 1.26                  | V     |

| V <sub>CCO</sub> <sup>(1)</sup> | Output driver supply voltage            | )                        |                          | 1.10 | _       | 3.60                  | V     |

| V <sub>CCAUX</sub>              | Auxiliary supply voltage <sup>(2)</sup> | V <sub>CCAUX</sub> = 2.5 |                          | 2.25 | 2.50    | 2.75                  | V     |

|                                 |                                         | V <sub>CCAUX</sub> = 3.3 |                          | 3.00 | 3.30    | 3.60                  | V     |

| V <sub>IN</sub> (3)             | Input voltage                           | PCI™ IOSTANDA            | RD                       | -0.5 | -       | V <sub>CCO</sub> +0.5 | V     |

|                                 | All other                               |                          | IP or IO_#               | -0.5 | _       | 4.10                  | V     |

|                                 |                                         | IOSTANDARDs              | IO_Lxxy_# <sup>(4)</sup> | -0.5 | -       | 4.10                  | V     |

| T <sub>IN</sub>                 | Input signal transition time(5          | 5)                       |                          | _    | _       | 500                   | ns    |

- 1. This  $V_{CCO}$  range spans the lowest and highest operating voltages for all supported I/O standards. Table 11 lists the recommended  $V_{CCO}$  range specific to each of the single-ended I/O standards, and Table 13 lists that specific to the differential standards.

- 2. Define V<sub>CCAUX</sub> selection using CONFIG VCCAUX constraint.

- 3. See XAPP459, Eliminating I/O Coupling Effects when Interfacing Large-Swing Single-Ended Signals to User I/O Pins on Spartan-3 Generation FPGAs.

- 4. For single-ended signals that are placed on a differential-capable I/O, V<sub>IN</sub> of –0.2V to –0.5V is supported but can cause increased leakage between the two pins. See *Parasitic Leakage* in <u>UG331</u>, *Spartan-3 Generation FPGA User Guide*.

- 5. Measured between 10% and 90% V<sub>CCO</sub>. Follow Signal Integrity recommendations.

# General DC Characteristics for I/O Pins

Table 9: General DC Characteristics of User I/O, Dual-Purpose, and Dedicated Pins (1)

| Symbol                         | Description                                                                                               | Test                                                                 | Conditions                              | Min  | Тур                   | Max   | Units |

|--------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------|------|-----------------------|-------|-------|

| I <sub>L</sub> <sup>(2)</sup>  | Leakage current at User I/O,<br>Input-only, Dual-Purpose, and<br>Dedicated pins, FPGA powered             | Driver is in a high-impeda $V_{IN} = 0V$ or $V_{CCO}$ max, so        | ance state,<br>ample-tested             | -10  | -                     | +10   | μА    |

| I <sub>HS</sub>                | Leakage current on pins during hot socketing, FPGA unpowered                                              | All pins except INIT_B, PROG_B, DONE, and JTAG pins when PUDC_B = 1. |                                         |      | -                     | +10   | μΑ    |

|                                |                                                                                                           | INIT_B, PROG_B, DONE when PUDC_B = 0.                                | , and JTAG pins or other pins           | Ad   | d I <sub>HS</sub> + I | RPU   | μΑ    |

| I <sub>RPU</sub> (3)           | Current through pull-up resistor                                                                          | V <sub>IN</sub> = GND                                                | $V_{CCO}$ or $V_{CCAUX} = 3.0V$ to 3.6V | -151 | -315                  | -710  | μΑ    |

|                                | at User I/O, Dual-Purpose,<br>Input-only, and Dedicated pins.<br>Dedicated pins are powered by<br>VCCAUX- |                                                                      | $V_{CCO}$ or $V_{CCAUX} = 2.3V$ to 2.7V | -82  | -182                  | -437  | μA    |

|                                |                                                                                                           |                                                                      | V <sub>CCO</sub> = 1.7V to 1.9V         | -36  | -88                   | -226  | μΑ    |

|                                |                                                                                                           |                                                                      | V <sub>CCO</sub> = 1.4V to 1.6V         | -22  | -56                   | -148  | μA    |

|                                |                                                                                                           |                                                                      | V <sub>CCO</sub> = 1.14V to 1.26V       | -11  | -31                   | -83   | μΑ    |

| R <sub>PU</sub> <sup>(3)</sup> | Equivalent pull-up resistor value                                                                         | V <sub>IN</sub> = GND                                                | V <sub>CCO</sub> = 3.0V to 3.6V         | 5.1  | 11.4                  | 23.9  | kΩ    |

|                                | at User I/O, Dual-Purpose,<br>Input-only, and Dedicated pins<br>(based on I <sub>RPU</sub> per Note 3)    |                                                                      | V <sub>CCO</sub> = 2.3V to 2.7V         | 6.2  | 14.8                  | 33.1  | kΩ    |

|                                |                                                                                                           |                                                                      | V <sub>CCO</sub> = 1.7V to 1.9V         | 8.4  | 21.6                  | 52.6  | kΩ    |

|                                |                                                                                                           |                                                                      | V <sub>CCO</sub> = 1.4V to 1.6V         | 10.8 | 28.4                  | 74.0  | kΩ    |

|                                |                                                                                                           |                                                                      | V <sub>CCO</sub> = 1.14V to 1.26V       | 15.3 | 41.1                  | 119.4 | kΩ    |

| I <sub>RPD</sub> (3)           | Current through pull-down                                                                                 | $V_{IN} = V_{CCO}$                                                   | V <sub>CCAUX</sub> = 3.0V to 3.6V       | 167  | 346                   | 659   | μΑ    |

|                                | resistor at User I/O, Dual-Purpose, Input-only, and Dedicated pins                                        |                                                                      | V <sub>CCAUX</sub> = 2.25V to 2.75V     | 100  | 225                   | 457   | μΑ    |

| R <sub>PD</sub> <sup>(3)</sup> | Equivalent pull-down resistor                                                                             |                                                                      |                                         | 5.5  | 10.4                  | 20.8  | kΩ    |

|                                | value at User I/O, Dual-Purpose, Input-only, and Dedicated pins                                           |                                                                      | V <sub>IN</sub> = 2.3V to 2.7V          | 4.1  | 7.8                   | 15.7  | kΩ    |

|                                | (based on I <sub>RPD</sub> per Note 3)                                                                    |                                                                      | V <sub>IN</sub> = 1.7V to 1.9V          | 3.0  | 5.7                   | 11.1  | kΩ    |

|                                |                                                                                                           |                                                                      | V <sub>IN</sub> = 1.4V to 1.6V          | 2.7  | 5.1                   | 9.6   | kΩ    |

|                                |                                                                                                           |                                                                      | V <sub>IN</sub> = 1.14V to 1.26V        | 2.4  | 4.5                   | 8.1   | kΩ    |

|                                |                                                                                                           | V <sub>CCAUX</sub> = 2.25V to                                        | V <sub>IN</sub> = 3.0V to 3.6V          | 7.9  | 16.0                  | 35.0  | kΩ    |

|                                |                                                                                                           | 2.75V                                                                | V <sub>IN</sub> = 2.3V to 2.7V          | 5.9  | 12.0                  | 26.3  | kΩ    |

|                                |                                                                                                           |                                                                      | V <sub>IN</sub> = 1.7V to 1.9V          | 4.2  | 8.5                   | 18.6  | kΩ    |

|                                |                                                                                                           |                                                                      | V <sub>IN</sub> = 1.4V to 1.6V          | 3.6  | 7.2                   | 15.7  | kΩ    |

|                                |                                                                                                           |                                                                      | V <sub>IN</sub> = 1.14V to 1.26V        | 3.0  | 6.0                   | 12.5  | kΩ    |

| I <sub>REF</sub>               | V <sub>REF</sub> current per pin                                                                          | All V <sub>CCO</sub> levels                                          |                                         | -10  | _                     | +10   | μA    |

| C <sub>IN</sub>                | Input capacitance                                                                                         | -                                                                    |                                         | -    | _                     | 10    | pF    |

| R <sub>DT</sub>                | Resistance of optional differential termination circuit                                                   | $V_{CCO} = 3.3V \pm 10\%$                                            | LVDS_33, MINI_LVDS_33,<br>RSDS_33       | 90   | 100                   | 115   | Ω     |

|                                | within a differential I/O pair. Not available on Input-only pairs.                                        | $V_{CCO} = 2.5V \pm 10\%$                                            | LVDS_25, MINI_LVDS_25,<br>RSDS_25       | 90   | 110                   | _     | Ω     |

- The numbers in this table are based on the conditions set forth in Table 8.

- For single-ended signals that are placed on a differential-capable I/O,  $V_{IN}$  of -0.2V to -0.5V is supported but can cause increased leakage between the two pins. See *Parasitic Leakage* in <u>UG331</u>, *Spartan-3 Generation FPGA User Guide*. This parameter is based on characterization. The pull-up resistance  $R_{PU} = V_{CCO}/I_{RPU}$ . The pull-down resistance  $R_{PD} = V_{IN}/I_{RPD}$ .

# **Quiescent Current Requirements**

Table 10: Quiescent Supply Current Characteristics

| Symbol              | Description                                 | Device     | Typical <sup>(2)</sup> | I-Grade<br>Maximum <sup>(2)</sup> | Q-Grade<br>Maximum <sup>(2)</sup> | Units |

|---------------------|---------------------------------------------|------------|------------------------|-----------------------------------|-----------------------------------|-------|

| I <sub>CCINTQ</sub> | Quiescent V <sub>CCINT</sub> supply current | XA3SD1800A | 41                     | 500                               | 900                               | mA    |

|                     |                                             | XA3SD3400A | 64                     | 725                               | _                                 | mA    |

| I <sub>ccoq</sub>   | Quiescent V <sub>CCO</sub> supply current   | XA3SD1800A | 0.4                    | 5                                 | 5                                 | mA    |

|                     |                                             | XA3SD3400A | 0.4                    | 5                                 | -                                 | mA    |

| I <sub>CCAUXQ</sub> | Quiescent V <sub>CCAUX</sub> supply current | XA3SD1800A | 25                     | 110                               | 145                               | mA    |

|                     |                                             | XA3SD3400A | 39                     | 160                               | -                                 | mA    |

- 1. The numbers in this table are based on the conditions set forth in Table 8.

- Quiescent supply current is measured with all I/O drivers in a high-impedance state and with all pull-up/pull-down resistors at the I/O pads disabled. Typical values are characterized using typical devices at room temperature (T<sub>J</sub> of 25°C at V<sub>CCINT</sub> = 1.2V, V<sub>CCO</sub> = 3.3V, and V<sub>CCAUX</sub> = 2.5V). The maximum limits are tested for each device at the respective maximum specified junction temperature and at maximum voltage limits with V<sub>CCINT</sub> = 1.26V, V<sub>CCO</sub> = 3.6V, and V<sub>CCAUX</sub> = 3.6V. The FPGA is programmed with a "blank" configuration data file (that is, a design with no functional elements instantiated). For conditions other than those described above (for example, a design including functional elements), measured quiescent current levels will be different than the values in the table.

- 3. There are two recommended ways to estimate the total power consumption (quiescent plus dynamic) for a specific design: a) The <a href="Spartan-3A DSP FPGA XPower Estimator">Spartan-3A DSP FPGA XPower Estimator</a> provides quick, approximate, typical estimates, and does not require a netlist of the design. b) XPower Analyzer uses a netlist as input to provide maximum estimates as well as more accurate typical estimates.

- 4. The maximum numbers in this table indicate the minimum current each power rail requires in order for the FPGA to power-on successfully.

- 5. For information on the power-saving Suspend mode, see XAPP480, Using Suspend Mode in Spartan-3 Generation FPGAs. Suspend mode typically saves 40% total power consumption compared to quiescent current.

# Single-Ended I/O Standards

Table 11: Recommended Operating Conditions for User I/Os Using Single-Ended Standards

| IOSTANDARD              | ν <sub>c</sub> | CO for Driver | ·s <sup>(2)</sup> |         | V <sub>REF</sub>                           |         | V <sub>IL</sub>          | V <sub>IH</sub> <sup>(3)</sup> |

|-------------------------|----------------|---------------|-------------------|---------|--------------------------------------------|---------|--------------------------|--------------------------------|

| Attribute               | Min (V)        | Nom (V)       | Max (V)           | Min (V) | Nom (V)                                    | Max (V) | Max (V)                  | Min (V)                        |

| LVTTL                   | 3.0            | 3.3           | 3.6               |         |                                            |         | 0.8                      | 2.0                            |

| LVCMOS33 <sup>(4)</sup> | 3.0            | 3.3           | 3.6               |         |                                            |         | 0.8                      | 2.0                            |

| LVCMOS25(4,5)           | 2.3            | 2.5           | 2.7               |         |                                            |         | 0.7                      | 1.7                            |

| LVCMOS18                | 1.65           | 1.8           | 1.95              |         | <sub>EF</sub> is not used<br>se I/O standa |         | 0.4                      | 0.8                            |

| LVCMOS15                | 1.4            | 1.5           | 1.6               |         | , o o a                                    |         | 0.4                      | 0.8                            |

| LVCMOS12                | 1.1            | 1.2           | 1.3               |         |                                            |         | 0.4                      | 0.7                            |

| PCI33_3 <sup>(6)</sup>  | 3.0            | 3.3           | 3.6               |         |                                            |         | 0.3 • V <sub>CCO</sub>   | 0.5 • V <sub>CCO</sub>         |

| HSTL_I                  | 1.4            | 1.5           | 1.6               | 0.68    | 0.75                                       | 0.9     | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1         |

| HSTL_III                | 1.4            | 1.5           | 1.6               | _       | 0.9                                        | -       | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1         |

| HSTL_I_18               | 1.7            | 1.8           | 1.9               | 0.8     | 0.9                                        | 1.1     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1         |

| HSTL_II_18              | 1.7            | 1.8           | 1.9               | -       | 0.9                                        | -       | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1         |

| HSTL_III_18             | 1.7            | 1.8           | 1.9               | -       | 1.1                                        | -       | V <sub>REF</sub> – 0.1   | V <sub>REF</sub> + 0.1         |

| SSTL18_I                | 1.7            | 1.8           | 1.9               | 0.833   | 0.900                                      | 0.969   | V <sub>REF</sub> – 0.125 | V <sub>REF</sub> + 0.125       |

| SSTL18_II               | 1.7            | 1.8           | 1.9               | 0.833   | 0.900                                      | 0.969   | V <sub>REF</sub> – 0.125 | V <sub>REF</sub> + 0.125       |

| SSTL2_I                 | 2.3            | 2.5           | 2.7               | 1.15    | 1.25                                       | 1.38    | V <sub>REF</sub> – 0.150 | V <sub>REF</sub> + 0.150       |

| SSTL2_II                | 2.3            | 2.5           | 2.7               | 1.15    | 1.25                                       | 1.38    | V <sub>REF</sub> – 0.150 | V <sub>REF</sub> + 0.150       |

| SSTL3_I                 | 3.0            | 3.3           | 3.6               | 1.3     | 1.5                                        | 1.7     | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2         |

| SSTL3_II                | 3.0            | 3.3           | 3.6               | 1.3     | 1.5                                        | 1.7     | V <sub>REF</sub> – 0.2   | V <sub>REF</sub> + 0.2         |

- Descriptions of the symbols used in this table are as follows:

- $V_{CCO}$  the supply voltage for output drivers  $V_{REF}$  the reference voltage for setting the input switching threshold  $V_{IL}$  the input voltage that indicates a Low logic level  $V_{IH}$  the input voltage that indicates a High logic level

- In general, the  $V_{CCO}$  rails supply only output drivers, not input circuits. The exceptions are for LVCMOS25 inputs when  $V_{CCAUX} = 3.3V$  range and for PCI I/O standards.

- For device operation, the maximum signal voltage (VIH max) can be as high as VIN max. See Table 4.

- There is approximately 100 mV of hysteresis on inputs using LVCMOS33 and LVCMOS25 I/O standards. 4.

- All Dedicated pins (PROG\_B, DONE, SUSPEND, TCK, TDI, TDO, and TMS) draw power from the  $V_{CCAUX}$  rail and use the LVCMOS25 or LVCMOS33 standard depending on  $V_{CCAUX}$ . The Dual-Purpose configuration pins use the LVCMOS25 standard before the User mode. When using these pins as part of a standard 2.5V configuration interface, apply 2.5V to the  $V_{CCO}$  lines of Banks 0, 1, and 2 at power-on as well as throughout configuration.

- For information on PCI IP solutions, see www.xilinx.com/pci. The PCI IOSTANDARD is not supported on input-only pins.

Table 12: DC Characteristics of User I/Os Using Single-Ended Standards

|                         |                   |                         | nditions                | Logic Level Characteristics |                            |  |

|-------------------------|-------------------|-------------------------|-------------------------|-----------------------------|----------------------------|--|

| IOSTANDARD              | Attribute         | I <sub>OL</sub><br>(mA) | I <sub>OH</sub><br>(mA) | V <sub>OL</sub><br>Max (V)  | V <sub>OH</sub><br>Min (V) |  |

| LVTTL <sup>(3)</sup>    | 2                 | 2                       | -2                      | 0.4                         | 2.4                        |  |

|                         | 4                 | 4                       | -4                      |                             |                            |  |

|                         | 6                 | 6                       | -6                      |                             |                            |  |

|                         | 8                 | 8                       | -8                      |                             |                            |  |

|                         | 12                | 12                      | -12                     |                             |                            |  |

|                         | 16                | 16                      | -16                     |                             |                            |  |

|                         | 24                | 24 <sup>(6)</sup>       | -24                     |                             |                            |  |

| LVCMOS33 <sup>(3)</sup> | 2                 | 2                       | -2                      | 0.4                         | V <sub>CCO</sub> - 0.4     |  |

|                         | 4                 | 4                       | -4                      |                             |                            |  |

|                         | 6                 | 6                       | -6                      |                             |                            |  |

|                         | 8                 | 8                       | -8                      |                             |                            |  |

|                         | 12                | 12                      | -12                     |                             |                            |  |

|                         | 16                | 16                      | -16 <sup>(6)</sup>      |                             |                            |  |

|                         | 24 <sup>(4)</sup> | 24                      | -24 <sup>(6)</sup>      |                             |                            |  |

| LVCMOS25 <sup>(3)</sup> | 2                 | 2                       | -2                      | 0.4                         | V <sub>CCO</sub> - 0.4     |  |

|                         | 4                 | 4                       | -4                      |                             |                            |  |

|                         | 6                 | 6                       | -6                      |                             |                            |  |

|                         | 8                 | 8                       | -8                      |                             |                            |  |

|                         | 12                | 12                      | -12                     |                             |                            |  |

|                         | 16 <sup>(4)</sup> | 16                      | -16 <sup>(6)</sup>      |                             |                            |  |

|                         | 24 <sup>(4)</sup> | 24 <sup>(6)</sup>       | -24 <sup>(6)</sup>      |                             |                            |  |

| LVCMOS18 <sup>(3)</sup> | 2                 | 2                       | -2                      | 0.4                         | V <sub>CCO</sub> - 0.4     |  |

|                         | 4                 | 4                       | -4                      |                             |                            |  |

|                         | 6                 | 6                       | -6 <sup>(6)</sup>       |                             |                            |  |

|                         | 8                 | 8                       | -8                      |                             |                            |  |

|                         | 12 <sup>(4)</sup> | 12                      | -12 <sup>(6)</sup>      |                             |                            |  |

|                         | 16 <sup>(4)</sup> | 16                      | -16                     |                             |                            |  |

| LVCMOS15 <sup>(3)</sup> | 2                 | 2                       | -2                      | 0.4                         | V <sub>CCO</sub> - 0.4     |  |

|                         | 4                 | 4                       | -4                      |                             |                            |  |

|                         | 6                 | 6                       | -6                      |                             |                            |  |

|                         | 8(4)              | 8                       | -8                      |                             |                            |  |

|                         | 12 <sup>(4)</sup> | 12                      | -12                     |                             |                            |  |

| LVCMOS12 <sup>(3)</sup> | 2                 | 2                       | -2                      | 0.4                         | V <sub>CCO</sub> - 0.4     |  |

|                         | 4 <sup>(4)</sup>  | 4                       | -4                      |                             |                            |  |

|                         | 6 <sup>(4)</sup>  | 6                       | -6                      |                             |                            |  |

| PCI33_3 <sup>(5)</sup>  |                   | 1.5                     | -0.5                    | 10% V <sub>CCO</sub>        | 90% V <sub>CCO</sub>       |  |

Table 12: DC Characteristics of User I/Os Using Single-Ended Standards (Cont'd)

|                           | Test Co                 | onditions               | Logic Level Characteristics |                            |  |

|---------------------------|-------------------------|-------------------------|-----------------------------|----------------------------|--|

| IOSTANDARD Attribute      | I <sub>OL</sub><br>(mA) | I <sub>OH</sub><br>(mA) | V <sub>OL</sub><br>Max (V)  | V <sub>OH</sub><br>Min (V) |  |

| HSTL_I <sup>(4)</sup>     | 8                       | -8                      | 0.4                         | V <sub>CCO</sub> - 0.4     |  |

| HSTL_III <sup>(4)</sup>   | 24 <sup>(7)</sup>       | -8                      | 0.4                         | V <sub>CCO</sub> - 0.4     |  |

| HSTL_I_18                 | 8                       | -8                      | 0.4                         | V <sub>CCO</sub> - 0.4     |  |

| HSTL_II_18 <sup>(4)</sup> | 16                      | -16 <sup>(7)</sup>      | 0.4                         | V <sub>CCO</sub> - 0.4     |  |

| HSTL_III_18               | 24 <sup>(7)</sup>       | -8                      | 0.4                         | V <sub>CCO</sub> - 0.4     |  |

| SSTL18_I                  | 6.7                     | -6.7                    | V <sub>TT</sub> – 0.475     | V <sub>TT</sub> + 0.475    |  |

| SSTL18_II <sup>(4)</sup>  | 13.4                    | -13.4                   | V <sub>TT</sub> – 0.475     | V <sub>TT</sub> + 0.475    |  |

| SSTL2_I                   | 8.1                     | -8.1                    | V <sub>TT</sub> – 0.61      | V <sub>TT</sub> + 0.61     |  |

| SSTL2_II <sup>(4)</sup>   | 16.2                    | -16.2                   | V <sub>TT</sub> – 0.80      | V <sub>TT</sub> + 0.80     |  |

| SSTL3_I                   | 8                       | -8                      | V <sub>TT</sub> – 0.6       | V <sub>TT</sub> + 0.6      |  |

| SSTL3_II                  | 16                      | -16                     | V <sub>TT</sub> – 0.8       | V <sub>TT</sub> + 0.8      |  |

- The numbers in this table are based on the conditions set forth in Table 8 and Table 11.

- Descriptions of the symbols used in this table are as follows:

- $I_{OL}$  the output current condition under which  $V_{OL}$  is tested

- $V_{OH}^{OH}$  the output current condition under which  $V_{OH}^{OH}$  is tested  $V_{OL}^{OH}$  the output voltage that indicates a Low logic level  $V_{OH}^{OH}$  the output voltage that indicates a High logic level

- V<sub>IL</sub> the input voltage that indicates a Low logic level

- VIH the input voltage that indicates a High logic level

- V<sub>CCO</sub> the supply voltage for output drivers

- $V_{\text{REF}}$  the reference voltage for setting the input switching threshold  $V_{\text{TT}}$  the voltage applied to a resistor termination

- For the LVCMOS and LVTTL standards: the same V<sub>OI</sub> and V<sub>OH</sub> limits apply for both the Fast and Slow slew attributes.

- These higher-drive output standards are supported only on FPGA banks 1 and 3. Inputs are unrestricted. See the chapter "Using I/O Resources" in UG331.

- Tested according to the relevant PCI specifications. For information on PCI IP solutions, see 5. http://www.xilinx.com/products/design\_resources/conn\_central/protocols/pci\_pcix.htm. The PCI IOSTANDARD is not supported on input-only pins. The PCIX IOSTANDARD is available and has equivalent characteristics, but no PCI-X IP is supported.

- Derate by 20% for T<sub>J</sub> above 100°C

- Derate by 5% for T<sub>.1</sub> above 100°C

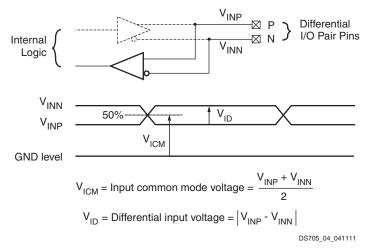

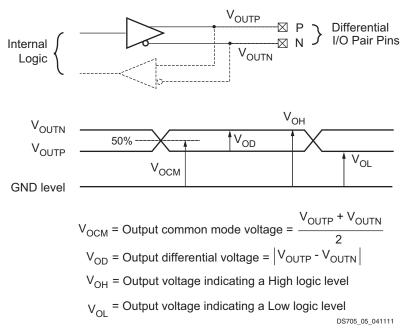

#### Differential I/O Standards

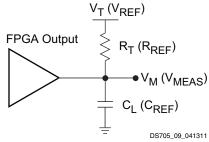

Figure 4: Differential Input Voltages

Table 13: Recommended Operating Conditions for User I/Os Using Differential Signal Standards

|                                | Vcc     | o for Drive | rs <sup>(1)</sup> |          | V <sub>ID</sub> |          |         | V <sub>ICM</sub> <sup>(2)</sup> |         |

|--------------------------------|---------|-------------|-------------------|----------|-----------------|----------|---------|---------------------------------|---------|

| IOSTANDARD Attribute           | Min (V) | Nom (V)     | Max (V)           | Min (mV) | Nom (mV)        | Max (mV) | Min (V) | Nom (V)                         | Max (V) |

| LVDS_25 <sup>(3)</sup>         | 2.25    | 2.5         | 2.75              | 100      | 350             | 600      | 0.3     | 1.25                            | 2.35    |

| LVDS_33 <sup>(3)</sup>         | 3.0     | 3.3         | 3.6               | 100      | 350             | 600      | 0.3     | 1.25                            | 2.35    |

| BLVDS_25 <sup>(4)</sup>        | 2.25    | 2.5         | 2.75              | 100      | 300             | -        | 0.3     | 1.3                             | 2.35    |

| MINI_LVDS_25 <sup>(3)</sup>    | 2.25    | 2.5         | 2.75              | 200      | -               | 600      | 0.3     | 1.2                             | 1.95    |

| MINI_LVDS_33 <sup>(3)</sup>    | 3.0     | 3.3         | 3.6               | 200      | -               | 600      | 0.3     | 1.2                             | 1.95    |

| LVPECL_25 <sup>(5)</sup>       |         | Inputs Only |                   | 100      | 800             | 1000     | 0.3     | 1.2                             | 1.95    |

| LVPECL_33 <sup>(5)</sup>       |         | Inputs Only |                   | 100      | 800             | 1000     | 0.3     | 1.2                             | 2.8(6)  |

| RSDS_25 <sup>(3)</sup>         | 2.25    | 2.5         | 2.75              | 100      | 200             | -        | 0.3     | 1.2                             | 1.5     |

| RSDS_33 <sup>(3)</sup>         | 3.0     | 3.3         | 3.6               | 100      | 200             | _        | 0.3     | 1.2                             | 1.5     |

| TMDS_33 <sup>(3,4,7)</sup>     | 3.14    | 3.3         | 3.47              | 150      | -               | 1200     | 2.7     | -                               | 3.23    |

| PPDS_25 <sup>(3)</sup>         | 2.25    | 2.5         | 2.75              | 100      | -               | 400      | 0.2     | -                               | 2.3     |

| PPDS_33 <sup>(3)</sup>         | 3.0     | 3.3         | 3.6               | 100      | -               | 400      | 0.2     | -                               | 2.3     |

| DIFF_HSTL_I_18                 | 1.7     | 1.8         | 1.9               | 100      | -               | -        | 0.8     | -                               | 1.1     |

| DIFF_HSTL_II_18 <sup>(8)</sup> | 1.7     | 1.8         | 1.9               | 100      | -               | -        | 0.8     | -                               | 1.1     |

| DIFF_HSTL_III_18               | 1.7     | 1.8         | 1.9               | 100      | -               | -        | 0.8     | -                               | 1.1     |

| DIFF_HSTL_I                    | 1.4     | 1.5         | 1.6               | 100      | -               | _        | 0.68    |                                 | 0.9     |

| DIFF_HSTL_III                  | 1.4     | 1.5         | 1.6               | 100      | -               | -        | -       | 0.9                             | _       |

| DIFF_SSTL18_I                  | 1.7     | 1.8         | 1.9               | 100      | -               | -        | 0.7     | -                               | 1.1     |

| DIFF_SSTL18_II <sup>(8)</sup>  | 1.7     | 1.8         | 1.9               | 100      | -               | _        | 0.7     | -                               | 1.1     |

| DIFF_SSTL2_I                   | 2.3     | 2.5         | 2.7               | 100      | -               | _        | 1.0     | -                               | 1.5     |

| DIFF_SSTL2_II(8)               | 2.3     | 2.5         | 2.7               | 100      | -               | _        | 1.0     | -                               | 1.5     |

| DIFF_SSTL3_I                   | 3.0     | 3.3         | 3.6               | 100      | -               | _        | 1.1     | _                               | 1.9     |

| DIFF_SSTL3_II                  | 3.0     | 3.3         | 3.6               | 100      | -               | _        | 1.1     | -                               | 1.9     |

- The V<sub>CCO</sub> rails supply only differential output drivers, not input circuits.

- V<sub>ICM</sub> must be less than V<sub>CCAUX</sub>.

These true differential output standards are supported only on FPGA banks 0 and 2. Inputs are unrestricted. See the chapter "Using I/O Resources" in UG331. 3.

- See External Termination Requirements for Differential I/O, page 16.

- LVPECL is supported on inputs only, not outputs. LVPECL\_33 requires  $V_{CCAUX} = 3.3V \pm 10\%$ .

- EVPECL\_33 maximum  $V_{ICM}$  = the lower of 2.8V or  $V_{CCAUX} (V_{ID}/2)$ . Requires  $V_{CCAUX} = 3.3V \pm 10\%$  for inputs.  $(V_{CCAUX} 300 \text{ mV}) \leq V_{ICM} \leq (V_{CCAUX} 37 \text{ mV})$ . These higher-drive output standards are supported only on FPGA banks 1 and 3. Inputs are unrestricted. See the chapter "Using I/O Resources" in UG331.  $V_{REF}$  inputs are used for the DIFF\_SSTL and DIFF\_HSTL standards. The  $V_{REF}$  settings are the same as for the single-ended versions in Table 11. Other differential standards do not use  $V_{REF}$

Figure 5: Differential Output Voltages

Table 14: DC Characteristics of User I/Os Using Differential Signal Standards

| IOSTANDARD Attribute |          | V <sub>OD</sub> |          |                          | V <sub>OCM</sub> |                          | V <sub>OH</sub>         | V <sub>OL</sub>         |

|----------------------|----------|-----------------|----------|--------------------------|------------------|--------------------------|-------------------------|-------------------------|

| IOSTANDARD Attribute | Min (mV) | Typ (mV)        | Max (mV) | Min (V)                  | Typ (V)          | Max (V)                  | Min (V)                 | Max (V)                 |

| LVDS_25              | 247      | 350             | 454      | 1.125                    | -                | 1.375                    | _                       | -                       |

| LVDS_33              | 247      | 350             | 454      | 1.125                    | -                | 1.375                    | _                       | -                       |

| BLVDS_25             | 240      | 350             | 460      | _                        | 1.30             | _                        | _                       | -                       |

| MINI_LVDS_25         | 300      | _               | 600      | 1.0                      | -                | 1.4                      | _                       | -                       |

| MINI_LVDS_33         | 300      | -               | 600      | 1.0                      | -                | 1.4                      | _                       | -                       |

| RSDS_25              | 100      | -               | 400      | 1.0                      | -                | 1.4                      | _                       | -                       |

| RSDS_33              | 100      | _               | 400      | 1.0                      | -                | 1.4                      | _                       | -                       |

| TMDS_33              | 400      | _               | 800      | V <sub>CCO</sub> - 0.405 | _                | V <sub>CCO</sub> - 0.190 | _                       | _                       |

| PPDS_25              | 100      | -               | 400      | 0.5                      | 0.8              | 1.4                      | _                       | -                       |

| PPDS_33              | 100      | -               | 400      | 0.5                      | 0.8              | 1.4                      | _                       | _                       |

| DIFF_HSTL_I_18       | -        | -               | -        | -                        | -                | _                        | V <sub>CCO</sub> - 0.4  | 0.4                     |

| DIFF_HSTL_II_18      | -        | -               | -        | -                        | -                | -                        | V <sub>CCO</sub> - 0.4  | 0.4                     |

| DIFF_HSTL_III_18     | -        | -               | -        | -                        | -                | -                        | V <sub>CCO</sub> - 0.4  | 0.4                     |

| DIFF_HSTL_I          | -        | -               | -        | -                        | -                | -                        | V <sub>CCO</sub> - 0.4  | 0.4                     |

| DIFF_HSTL_III        | -        | -               | -        | -                        | -                | -                        | V <sub>CCO</sub> - 0.4  | 0.4                     |

| DIFF_SSTL18_I        | -        | -               | -        | -                        | -                | -                        | V <sub>TT</sub> + 0.475 | V <sub>TT</sub> – 0.475 |

| DIFF_SSTL18_II       | -        | -               | -        | -                        | -                | -                        | V <sub>TT</sub> + 0.475 | V <sub>TT</sub> – 0.475 |

| DIFF_SSTL2_I         | -        | -               | -        | _                        | -                | -                        | V <sub>TT</sub> + 0.61  | V <sub>TT</sub> – 0.61  |

| DIFF_SSTL2_II        | -        | -               | -        | -                        | -                | -                        | V <sub>TT</sub> + 0.81  | V <sub>TT</sub> – 0.81  |

| DIFF_SSTL3_I         | _        | -               | -        | -                        | -                | -                        | V <sub>TT</sub> + 0.6   | V <sub>TT</sub> – 0.6   |

| DIFF_SSTL3_II        | -        | _               | _        | _                        | _                | _                        | V <sub>TT</sub> + 0.8   | V <sub>TT</sub> – 0.8   |

- The numbers in this table are based on the conditions set forth in Table 8 and Table 13. 1.

- 2.

- See External Termination Requirements for Differential I/O, page 16. Output voltage measurements for all differential standards are made with a termination resistor ( $R_T$ ) of 100 $\Omega$  across the N and P pins of the 3.

- At any given time, no more than two of the following differential output standards can be assigned to an I/O bank: LVDS\_25, RSDS\_25, MINI\_LVDS\_25, PPDS\_25 when V<sub>CCO</sub>=2.5V, or LVDS\_33, RSDS\_33, MINI\_LVDS\_33, TMDS\_33, PPDS\_33 when V<sub>CCO</sub> = 3.3V.

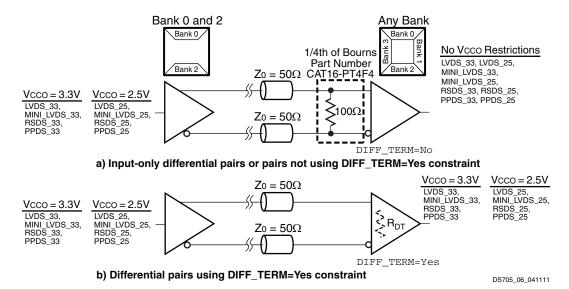

#### External Termination Requirements for Differential I/O

#### LVDS, RSDS, MINI LVDS, and PPDS I/O Standards

Figure 6: External Input Termination for LVDS, RSDS, MINI\_LVDS, and PPDS I/O Standards

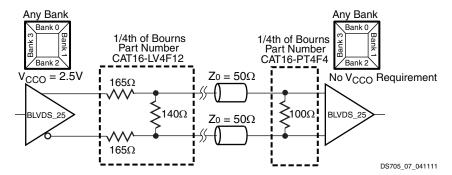

#### BLVDS 25 I/O Standard

Figure 7: External Output and Input Termination Resistors for BLVDS 25 I/O Standard

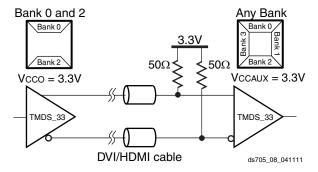

#### TMDS\_33 I/O Standard

Figure 8: External Input Resistors Required for TMDS\_33 I/O Standard

#### **Device DNA Read Endurance**

Table 15: Device DNA Identifier Memory Characteristics

| Symbol     | Description                                                                                        | Minimum    | Units          |

|------------|----------------------------------------------------------------------------------------------------|------------|----------------|

| DNA_CYCLES | Number of READ operations or JTAG ISC_DNA read operations. Unaffected by HOLD or SHIFT operations. | 30,000,000 | Read<br>cycles |

# **Switching Characteristics**

All XA Spartan-3A DSP FPGAs ship in the -4 speed grade. Switching characteristics in this document are designated as Production, as shown in Table 16.

**Production**: These specifications are approved once enough production silicon of a particular device family member has been characterized to provide full correlation between speed files and devices over numerous production lots. There is no under-reporting of delays, and customers receive formal notification of any subsequent changes.

# **Software Version Requirements**

Production-quality systems must use FPGA designs compiled using a speed file designated as PRODUCTION status. FPGAs designs using a less mature speed file designation should only be used during system prototyping or pre-production qualification. FPGA designs with speed files designated as Preview, Advance, or Preliminary should not be used in a production-quality system.

Whenever a speed file designation changes, as a device matures toward Production status, rerun the latest Xilinx ISE software on the FPGA design to ensure that the FPGA design incorporates the latest timing information and software updates.

All parameter limits are representative of worst-case supply voltage and junction temperature conditions. Unless otherwise noted, the published parameter values apply to all XA Spartan-3A DSP devices. AC and DC characteristics are specified using the same numbers for both I-Grade and Q-Grade.

Create a Xilinx user account and sign up to receive automatic e-mail notification whenever this data sheet or the associated user guides are updated.

Sign Up for Alerts on Xilinx.com

http://www.xilinx.com/support/answers/18683.htm

Timing parameters and their representative values are selected for inclusion below either because they are important as general design requirements or they indicate fundamental device performance characteristics. The XA Spartan-3A DSP FPGA speed files (v1.32), part of the Xilinx Development Software, are the original source for many but not all of the values. The speed grade designations for these files are shown in Table 16. For more complete, more precise, and worst-case data, use the values reported by the Xilinx static timing analyzer (TRACE in the Xilinx development software) and back-annotated to the simulation netlist.

Table 16: XA Spartan-3A DSP FPGA v1.32 Speed Grade Designations

| Device     | Production |

|------------|------------|

| XA3SD1800A | -4         |

| XA3SD3400A | -4         |

Table 17 provides the recent history of the XA Spartan-3A DSP FPGA speed files.

Table 17: XA Spartan-3A DSP Speed File Version History

| Versio | ISE Software Release | Description             |

|--------|----------------------|-------------------------|

| 1.32   | ISE 10.1 SP2         | Support for Automotive. |

## I/O Timing

#### Pin-to-Pin Clock-to-Output Times

Table 18: Pin-to-Pin Clock-to-Output Times for the IOB Output Path

| Symbol                | Description                                                                                                           | Conditions                                                | Device     | Speed Grade: -4 Max | Units |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------|---------------------|-------|

| Clock-to-Out          | put Times                                                                                                             |                                                           |            |                     |       |

| T <sub>ICKOFDCM</sub> | T <sub>ICKOFDCM</sub> When reading from the Output Flip-Flop (OFF), the time from the active transition on the Global |                                                           | XA3SD1800A | 3.51                | ns    |

|                       | Clock pin to data appearing at the Output pin. The DCM is in use.                                                     |                                                           | XA3SD3400A | 3.82                | ns    |

| T <sub>ICKOF</sub>    | When reading from OFF, the time from the active transition on the Global Clock pin to data                            | LVCMOS25 <sup>(2)</sup> , 12mA<br>output drive, Fast slew | XA3SD1800A | 5.58                | ns    |

|                       | appearing at the Output pin. The DCM is not in use.                                                                   | rate, without DCM                                         | XA3SD3400A | 6.13                | ns    |

#### Notes:

- 1. The numbers in this table are tested using the methodology presented in Table 27 and are based on the operating conditions set forth in Table 8 and Table 11.

- 2. This clock-to-output time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or a standard other than LVCMOS25 with 12 mA drive and Fast slew rate is assigned to the data Output. If the former is true, *add* the appropriate Input adjustment from Table 23. If the latter is true, *add* the appropriate Output adjustment from Table 26.

- 3. DCM output jitter is included in all measurements.

# Pin-to-Pin Setup and Hold Times

Table 19: Pin-to-Pin Setup and Hold Times for the IOB Input Path (System Synchronous)

| Cumbal             | Description                                                                                      | Conditions                                      | Device     | Speed Grade: -4 | Unito |

|--------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------|------------|-----------------|-------|

| Symbol             | Description Conditions                                                                           |                                                 | Device     | Min             | Units |

| Setup Times        |                                                                                                  |                                                 |            |                 |       |

| T <sub>PSDCM</sub> | When writing to the Input Flip-Flop (IFF), the time from the setup of data at the Input pin to   | LVCMOS25 <sup>(2)</sup> ,<br>IFD_DELAY_VALUE=0, | XA3SD1800A | 3.11            | ns    |

|                    | the active transition at a Global Clock pin. The DCM is in use. No Input Delay is programmed.    | with DCM <sup>(4)</sup>                         | XA3SD3400A | 2.49            | ns    |

| T <sub>PSFD</sub>  | When writing to IFF, the time from the setup of data at the Input pin to an active transition at | LVCMOS25 <sup>(2)</sup> ,<br>IFD_DELAY_VALUE=6, | XA3SD1800A | 3.39            | ns    |

|                    | the Global Clock pin. The DCM is not in use. The Input Delay is programmed.                      | without DCM                                     | XA3SD3400A | 3.08            | ns    |

| Hold Times         |                                                                                                  |                                                 |            |                 |       |

| T <sub>PHDCM</sub> | When writing to IFF, the time from the active transition at the Global Clock pin to the point    | LVCMOS25 <sup>(3)</sup> ,<br>IFD_DELAY_VALUE=0, | XA3SD1800A | -0.38           | ns    |

|                    | when data must be held at the Input pin. The DCM is in use. No Input Delay is programmed.        | with DCM <sup>(4)</sup>                         | XA3SD3400A | -0.26           | ns    |

| T <sub>PHFD</sub>  | When writing to IFF, the time from the active transition at the Global Clock pin to the point    | LVCMOS25 <sup>(3)</sup> ,<br>IFD_DELAY_VALUE=6, | XA3SD1800A | -0.71           | ns    |

|                    | when data must be held at the Input pin. The DCM is not in use. The Input Delay is programmed.   | without DCM                                     | XA3SD3400A | -0.65           | ns    |

#### Notes:

- 1. The numbers in this table are tested using the methodology presented in Table 27 and are based on the operating conditions set forth in Table 8 and Table 11.

- This setup time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data Input. If this is true of the Global Clock Input, subtract the appropriate adjustment from Table 23. If this is true of the data Input, add the appropriate Input adjustment from the same table.

- 3. This hold time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data Input. If this is true of the Global Clock Input, add the appropriate Input adjustment from Table 23. If this is true of the data Input, subtract the appropriate Input adjustment from the same table. When the hold time is negative, it is possible to change the data before the clock's active edge.

- DCM output jitter is included in all measurements.

18

# **Input Setup and Hold Times**

Table 20: Setup and Hold Times for the IOB Input Path

| Symbol               | Description                                                                                         | Conditions              | IFD_DELAY<br>_VALUE | Device     | Speed Grade: -4<br>Min | Units |    |

|----------------------|-----------------------------------------------------------------------------------------------------|-------------------------|---------------------|------------|------------------------|-------|----|

| Setup Tim            | es                                                                                                  |                         |                     |            |                        |       |    |

| T <sub>IOPICK</sub>  | Time from the setup of data at the Input pin to                                                     | LVCMOS25 <sup>(2)</sup> | 0                   | XA3SD1800A | 1.81                   | ns    |    |

|                      | the active transition at the ICLK input of the Input Flip-Flop (IFF). No Input Delay is programmed. |                         |                     | XA3SD3400A | 1.88                   | ns    |    |

| T <sub>IOPICKD</sub> | Time from the setup of data at the Input pin to                                                     | LVCMOS25(2)             | 1                   | XA3SD1800A | 2.24                   | ns    |    |

|                      | the active transition at the ICLK input of the Input Flip-Flop (IFF). The Input Delay is            |                         | 2                   |            | 2.83                   | ns    |    |

|                      | programmed.                                                                                         |                         | 3                   |            | 3.64                   | ns    |    |

|                      |                                                                                                     |                         | 4                   |            | 4.20                   | ns    |    |

|                      |                                                                                                     |                         | 5                   |            | 4.16                   | ns    |    |

|                      |                                                                                                     |                         | 6                   |            | 5.09                   | ns    |    |

|                      |                                                                                                     |                         |                     | 7          |                        | 6.02  | ns |

|                      |                                                                                                     |                         | 8                   |            | 6.63                   | ns    |    |

|                      |                                                                                                     |                         | 1                   | XA3SD3400A | 2.44                   | ns    |    |