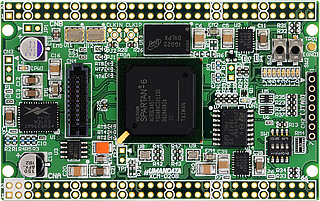

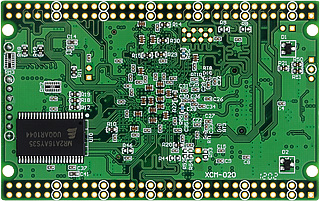

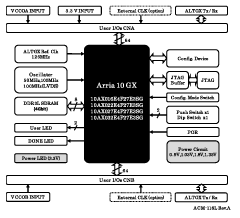

FPGA overview XC7A200T Logic Cell 215,360 Slice 33,650 Max Distributed RAM (kb) 2,888 Max Block RAM (kb) 13,140 DSP Slice 740 CMT (MMCMx1 + PLLx1) Ten GTP Channel (Device) 16 GTP Channel ( Board ) Four Max user I / O (Device) 500 Max user I / O ( Board ) 296 For details on the FPGA overview, see the XILINX Artix-7 page .

- Equipped with XC7A200T-1FFG1156C

- User I / O:

29 6 IOA (CNA connector): 64 Vcco = 3.3V

IOB (CNB connector): 64 Vcco = External input

IOC (CNC connector): 84 Vcco = External input

IOD (CND connector): 84 This Vcco = external inputIOA IOB IOC IOD A board MAX

40.4mm MIN 25.5mmMAX 34.2mm

MIN 24.7mmMAX 46.8mm

MIN 27.2mmMAX 50.6mm

MIN 23.1mm- Not all I / O is LVDS compatible

- Users are requested to consider each I / O standard based on FPGA materials.

- 3.3V single power supply operation

1.0V, 1.2V, 1.5V, 1.8V, 2.5V generated in board

Power sequencer installed (when turned on ) - RocketIO (GTP) Evaluable From

CNA / CNB TX / RX 2ch each, total 4ch

Reference clock: 125MHz (LVDS), external input possible (MMCX) - DDR3 SDRAM installed

MT41K64M16 (Micron, 1Gbit)

Custom-made 4Gbit available - Configuration ROM

MT25QL128ABA1ESE-0SIT (Micron, 128Mbit) - Onboard clock

50MHz (LVTTL), 200MHz (LVDS)

can be supplied externally - General purpose LED x2

- General-purpose switch x2

Push button x1

DIP switch x1bit

Configuration to FPGA with 7-pin JTAG connector

ISP

JTAG Buffer circuit to configuration ROM for stable download- Status LED: CONF_DONE (blue), POWER LED (red)

- Equipped with a reset circuit for configuration

- 10-layer board

- Board dimensions: 54mm x 86mm Credit card size

- RoHS directive compliant

RoHS directive compliant

RoHS directive compliant